# (10 Gigabit Small Form Factor Pluggable Module)

Revision 3.1 Adopted Revision Copyright © 2002, 2003 by XFP Promoters See copyright notice for restrictions.

Technical Editor:

Ali Ghiasi Broadcom Corporation 3151 Zanker Road San Jose, CA 95134 Voice:(408) 922-7423 EMail: aghiasi@broadcom.com XFP Chair:

Robert Snively Brocade Communication Systems, Inc. 1745 Technology Drive San Jose, CA 95110 Voice (408) 487-8135 EMail: rsnively@brocade.com

### Legal Disclaimer

This specification has been formally adopted by the XFP Promoters. Changes to the document may be made to correct any errata in the specification, including clarifications and other changes. Verify that you are using the latest revision of the specification by visiting the XFP web-site at www.xfpmsa.org.

The promoters of the XFP specification, Broadcom Corporation, Brocade Communications Systems, Inc., Ciena Corporation, Emulex Corporation, Finisar Corporation, JDS Uniphase Corporation, Innovation Core SEI, Inc., Maxim Integrated Products, Tyco Electronics Corporation, and Velio Communication ("XFP Promoters"), and many contributors, collaborated to develop a specification for a 10 Gigabit small foot print pluggable module. The promoters stated a wish to encourage broad and rapid industry adoption of the specification. This specification is the result of such collaboration. The XFP specification may be offered to formal standards bodies to further support the adoption of the specification.

THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE. THE XFP PROMOTERS DISCLAIM ALL LIABILITY, INCLUDING LIABILITY FOR IN-FRINGEMENT OF ANY PROPRIETARY RIGHTS, RELATING TO USE OF INFORMATION IN THIS SPEC-IFICATION. IN NO EVENT SHALL THE XFP PROMOTERS, CONTRIBUTORS OR ADOPTERS BE LIABLE FOR ANY DIRECT, INDIRECT, SPECIAL, EXEMPLARY, PUNITIVE, OR CONSEQUENTIAL DAMAGES, INCLUDING, WITHOUT LIMITATION, LOST PROFITS, EVEN IF ADVISED OF THE POSSI-BILITY OF SUCH DAMAGES.

This specification may contain, and sometimes even require the use of, intellectual property owned by others. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein, except as indicated in the following copyright notice. Rights to certain of such intellectual property may be provided by the XFP Promoters Agreement, XFP Adopters Agreement and the XFP Contributors Addendum.

### **Copyright Notice**

Copyright owned by XFP Promoters. XFP Promoters are Broadcom Corporation, Brocade Communications Systems, Inc., Ciena Corporation, Emulex Corporation, Finisar Corporation, JDS Uniphase Corporation, Innovation Core SEI, Inc., Maxim Integrated Products, Tyco Electronics Corporation, and Velio Communication. All rights are reserved except that a license is hereby granted to copy and reproduce this specification, in unmodified form only, for fee-free distribution or for use internal to the organization copying the specification.

### **Identification of defects**

If errors are identified in this specification, please notify the chair and editor identified on the first page. Please provide a clear identification of the error, the text of any proposed correction, and a justification or explanation of the correction.

### **Publication History**

| Revision<br>Number | Description                                  | Date     |

|--------------------|----------------------------------------------|----------|

| 0.1                | Initial Publication of Document, Preliminary | 3/27/02  |

| 0.5                | First full draft                             | 4/11/02  |

| 0.7                | Second full draft                            | 5/23/02  |

| 0.8                | Third full draft                             | 6/21/02  |

| 0.9                | Pre-Public Release 0                         | 7/15/02  |

| 0.91               | Pre-Public Release 1                         | 7/16/02  |

| 0.92               | 1st-Public Release                           | 7/19/02  |

| 0.93               | Pre-Meeting Editing Draft                    | 8/21/02  |

| 0.95               | Internal draft                               | 09/21/02 |

| 0.99               | 2nd pre-Public Release                       | 10/31/02 |

| 1.0                | Pre-Ratification Draft                       | 12/2/02  |

| 2.0                | Adoption Draft                               | 12/16/02 |

| 3.0                | Adopted Specification                        | 3/3/03   |

| 3.1                | Modified Copyright Statement                 | 4/2/03   |

### Foreword

The XFP Promoters, Broadcom Corporation, Brocade Communications Systems, Inc., Ciena Corporation, Emulex Corporation, Finisar Corporation, nnovation Core SEI, Inc. (a Sumitomo Electric Company), JDS Uniphase Corporation, I Maxim Integrated Products, Tyco Electronics Corporation, Velio Communication, and many contributors gathered together to develop a specification for a 10 Gigabit small foot print pluggable module. The Promoters stated a wish to encourage broad and rapid industry adoption of the specification. The XFP specification may be offered to formal standards bodies to further support the adoption of the specification. The XFP Promoters and Contributors solicited technical review and contributions to the XFP specification among many component, module, and system designers and manufacturers to assure that it meets a broad variety of requirements.

Signed agreements exist among the promoters and between the promoters and contributors that allowed them to carry forward these activities in a manner that encouraged rapid development, open sharing of technology, and the timely resolution of disagreements. The agreements further explained and protected the rights of both promoters and contributors. Similar agreements protect the rights of adopters of the specification.

Organizations may become adopters of the XFP specification by contacting any XFP Promoter and requesting the necessary forms and following the required procedures.

| Accelerant Networks        | Marvell Semiconductor, Inc.      |

|----------------------------|----------------------------------|

| Aeluros                    | Mathstar, Inc.                   |

| Agere Systems              | McData                           |

| Agilent Technologies, Inc. | MergeOptics GmbH                 |

| Alcatel Optronics          | Micrel Semiconductor, Inc.       |

| AMCC                       | Mindspeed Technologies           |

| Ample Communications       | Mitsubishi Electric              |

| Analog Devices, Inc.       | Modulight, Inc.                  |

| ASIP, Inc.                 | Molex, Inc.                      |

| ASTRI                      | Multilink Technology Corporation |

| Atrica                     | NEC Corporation                  |

### **XFP Contributors**

| Avalon Photonics, Ltd.                              | NEL Corporation                                       |

|-----------------------------------------------------|-------------------------------------------------------|

| Big Bear Networks                                   | Network Elements, Inc.                                |

| BitBlitz Communications                             | NTT                                                   |

| CENiX                                               | OEpic, Inc.                                           |

| Cortina Systems                                     | OpNext                                                |

| E2O Communications Inc.                             | Optical Communication Products, Inc.                  |

| EMC Corporation                                     | Optium Corporation                                    |

| Emcore Corporation                                  | OptoIC Technology                                     |

| Force 10 Networks, Inc.                             | Optronix, Inc.                                        |

| Foxconn Electronics, Inc.                           | Picolight, Inc.                                       |

| Fourte' Design and Development                      | Pine Photonics Communications, Inc.                   |

| Fujitsu                                             | PMC-Sierra                                            |

| Gennum Corporation                                  | Primarion                                             |

| GTRAN, Inc.                                         | Phyworks Limited                                      |

| HARTING Electro-Optics                              | Qlogic, Inc.                                          |

| Hitachi Cable America, Inc.                         | Quake Technologies                                    |

| Ignis Optics, Inc.                                  | RF Micro Devices                                      |

| Industrial Technology Research Institute            | Samsung Electronics Company, Ltd.                     |

| Infineon Technologies                               | Sigma-Links, Inc. (an OKI and Fujikura joint venture) |

| Infinera Corporation                                | Silicon Bridge, Inc.                                  |

| Intel Corporation                                   | Spirent Communications                                |

| I-TECH Corporation                                  | Stratos Lightwave, Inc.                               |

| KeyEye Communications                               | Sun MicroSystems, Inc.                                |

| Kodeos Communications                               | Vitesse Semiconductor Corporation                     |

| Lattice Semiconductor Corporation                   | Wuhan Telecommunication Devices Co.                   |

| LSI Logic Corporation                               | Xilinx, Inc.                                          |

| Luminent, Inc. (an MRV Communications Com-<br>pany) |                                                       |

### Acknowledgments

The XFP members would like to acknowledge and thank Dr. Ali Ghiasi for his tremendous effort and diligence in editing this specification.

The members would like to thank Dr. Lew Aronson and Mr. Ed Bright for writing the Management and Mechanical chapters. In addition, they would like to thank Mr. Tom Lindsay for the jitter Appendix, Dr. Piero Bradley for jitter section, Mr. Lawrence Williams for the XFI Channel Simulation and Modeling and the Optimum Via Appendix, Mr. Henrik Johansen for the compliance test boards Appendix, Mr. Steve Silverman for the power supply section, Mr. Gary Heitkamp for the Thermal Appendix, Mr. Randy Clark for the 2-Wire Protocol, Mr. Ron Miller for the TDR Appendix, and Dr. Stefanos Sidiropoulos for the VPS section.

The members would also like to thank Mr. Robert Snively for skillfully steering the MSA, as without him we could not have achieved our goal.

Special thanks are due to all those who attended the meetings and made contributions, as this document is a collection of their work.

### **Table of Contents**

| Chap  | ter 1:         | Scope of XFP specification                                           | 1  |

|-------|----------------|----------------------------------------------------------------------|----|

| 1.1   | Introdu        | iction                                                               | 1  |

| 1.2   | Requir         | ements on Press announcements                                        | 2  |

| Chap  | ter 2:         | XFP Electrical Interface                                             | 3  |

| 2.1   | Introdu        | lction                                                               | 3  |

| 2.2   | Genera         | al Requirements                                                      | 3  |

| 2.3   | XFP H          | ost Connector Definition                                             | 3  |

| 2.4   | Low S          | peed Electrical Hardware Pins                                        | 6  |

|       | 2.4.1          | Mod_NR                                                               |    |

|       | 2.4.2          | Mod_DeSel                                                            | 6  |

|       | 2.4.3          | Interrupt                                                            | 7  |

|       | 2.4.4          | TX_DIS                                                               | 7  |

|       | 2.4.5          | Mod_ABS                                                              | 7  |

|       | 2.4.6          | RX_LOS                                                               | 7  |

|       | 2.4.7          | P_Down/RST                                                           | 7  |

|       |                | 2.4.7.1 Power Down Function                                          | 7  |

|       |                | 2.4.7.2 Reset Function                                               |    |

|       |                | 2.4.7.3 Module Behavior during Power Down and Reset                  |    |

| 2.5   |                | peed Electrical Specifications                                       |    |

| 2.6   | Timing         | Requirement of Control and Status I/O                                | 10 |

| 2.7   | XFP P          | ower Requirement                                                     | 11 |

|       | 2.7.1          | Power Noise Output                                                   | 11 |

|       | 2.7.2          | Power Noise Susceptibility                                           |    |

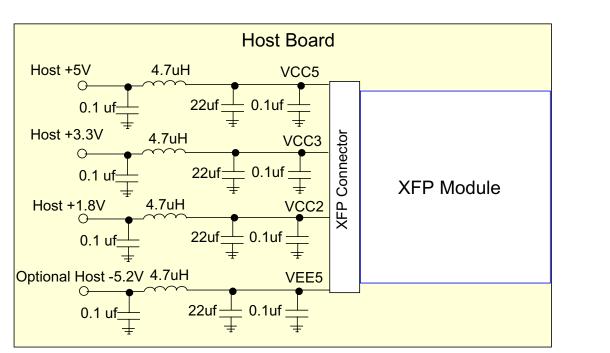

|       | 2.7.3          | Host Filtering                                                       | 13 |

| 2.8   | ESD            |                                                                      | 15 |

| Chap  | ter 3:         | High Speed Electrical Specification XFI                              | 16 |

| 3.1 · |                | iction                                                               |    |

| 3.2   |                | plications Definition                                                |    |

| 3.3   | •              | rmination and DC Blocking                                            |    |

| 3.4   |                | mpliance Channel                                                     |    |

| 3.5   |                | SIC/SerDes Specification                                             |    |

| 5.5   | 3.5.1          | XFI ASIC/SerDes Transmitter Output Specifications at A (Informative) |    |

|       | 3.5.1<br>3.5.2 | XFI ASIC/SerDes Receiver Input Specifications at D (Informative)     |    |

| 3.6   |                | est System Specification                                             |    |

| 0.0   | 3.6.1          | XFI Host Transmitter Output Specifications at B                      |    |

|       | J.U. I         |                                                                      | ∠0 |

| 3.7    | XFI Mod    | lule Specifications                                                   |                    |

|--------|------------|-----------------------------------------------------------------------|--------------------|

|        | 3.7.1      | XFI Module Transmitter Input Specifications at B'                     |                    |

|        | 3.7.2      | XFI Module Receiver Output Specifications at C'                       |                    |

| 3.8    | Signal C   | Conditioner                                                           |                    |

|        | 3.8.1      | Telecom Module                                                        |                    |

|        | 3.8.2      | Datacom Module                                                        |                    |

| 3.9    | Reference  | ce Clock Specifications                                               | 40 7               |

|        | 3.9.1      | Optional Synchronous CMU Clock                                        |                    |

| Chapte | er 4: )    | XFP 2-Wire Interface Protocol                                         | 9<br><b>42</b> 10  |

| 4.1    | Introduc   | tion                                                                  |                    |

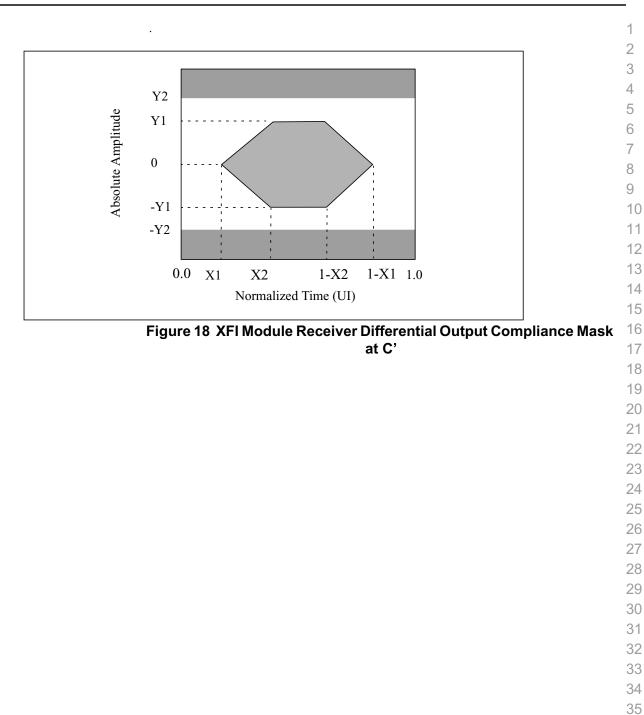

| 4.2    | XFP 2-V    | Vire Timing Diagram                                                   |                    |

| 4.3    |            | Transaction Timing                                                    |                    |

| 4.4    | -          | Addressing and Operation                                              |                    |

| 4.5    |            | rite Functionality                                                    | . –                |

|        | 4.5.1      | Packet Error Checking                                                 | 10                 |

|        | 4.5.2      | XFP Memory Address Counter (Read and Write Operations)                | 47                 |

|        | 4.5.3      | Read Operations (Current Address Read)                                | 4.0                |

|        | 4.5.4      | Read Operations (Random Read)                                         | 4.0                |

|        | 4.5.5      | Read Operations (Sequential Read)                                     |                    |

|        | 4.5.6      | Read Operation Packet Error Checking                                  |                    |

|        | 4.5.7      | Write Operations (Byte Write)                                         |                    |

|        | 4.5.8      | Write Operations (Sequential Write)                                   |                    |

|        | 4.5.9      | Write Operation Packet Error Checking                                 |                    |

|        | 4.5.10     | Write Operations (Acknowledge Polling)                                | <b>53</b> 25<br>26 |

| Chapte | er 5: I    | Management interface                                                  |                    |

|        | 5.0.1      | Applicable Documents                                                  |                    |

| 5.1    | Descript   | ion of Lower Memory Map: Control Functions, Diagnostics, Table Access | 57 29              |

| 5.2    | Identifier | ٢                                                                     |                    |

| 5.3    | Signal C   | Conditioner Control                                                   | 58 31              |

| 5.4    | 2-Wire S   | Serial Interface Checksum                                             | 60 32              |

| 5.5    | Table Se   | election and Password Entry ( <u>Table 44</u> )                       | 60 <sup>33</sup>   |

| 5.6    |            | onitoring Functions                                                   | 61 <sup>34</sup>   |

| 5.7    |            | Variable Power Supply (VPS) Control                                   | 63 <sup>35</sup>   |

| 5.8    | •          | BER Reporting                                                         |                    |

| 5.9    | -          | ngth Control                                                          | 66 37              |

| 5.10   |            | ntrol                                                                 | 67 38              |

| 5.11   |            | System Logic                                                          | 60                 |

| 0.11   | 5.11.1     | General Control and Status Bits                                       | 60                 |

|        | 0.11.1     |                                                                       | 41                 |

|        |            |                                                                       | 42                 |

| 5.12   | Timing for Soft Control and Status Functions                                 | 70 1            |

|--------|------------------------------------------------------------------------------|-----------------|

| 5.13   | Description of Upper Memory Map Table 00h – Future Diagnostics Functions     | 80 2            |

| 5.14   | Description of Upper Memory Map Table 01h – Serial ID Memory Map             | -               |

| 5.15   | Identifier                                                                   | 81 4            |

| 5.16   | Extended Identifier                                                          | 82 5            |

| 5.17   | Connector                                                                    | 6               |

| 5.18   | Interface Specification                                                      | 7               |

| 5.19   | Encoding                                                                     | 85 <sup>8</sup> |

| 5.20   | BR, Minimum                                                                  | 86 9            |

| 5.21   | BR, maximum                                                                  | ار<br>86        |

| 5.22   | Length (Standard single mode fiber)-km                                       | I               |

| 5.23   | Length (Extended Bandwidth 50 mm Multimode Fiber)                            | I               |

| 5.24   | Length (50 um Multimode Fiber)                                               | 1               |

| 5.25   | Length (62.5 um Multimode Fiber)                                             | 1               |

| 5.26   | Length (Copper)                                                              |                 |

| 5.27   | Device Technology                                                            |                 |

| 5.28   | Vendor name                                                                  |                 |

| 5.29   | CDR Support                                                                  |                 |

| 5.30   | Vendor OUI                                                                   | 0               |

| 5.31   | Vendor PN                                                                    | 0               |

| 5.32   | Vendor Rev                                                                   | 2               |

| 5.33   | Laser Wavelength                                                             | 90 2            |

| 5.34   | Laser Wavelength Tolerance                                                   | 90 2            |

| 5.35   | Maximum Case Temperature                                                     | 91 2            |

| 5.36   | CC BASE                                                                      | 01              |

| 5.37   | Power supply requirements                                                    |                 |

| 5.38   | Vendor SN                                                                    | ∠               |

| 5.39   | Date Code                                                                    | 93 3            |

| 5.40   | Diagnostic Monitoring Type                                                   |                 |

| 5.41   | Enhanced Options                                                             | -               |

| 5.42   | Auxiliary Monitoring                                                         |                 |

| 5.43   | CC_EXT                                                                       |                 |

| 5.44   | Vendor Specific ID Field                                                     |                 |

| 5.45   | Description of Upper Memory Map Table 02h – User EEPROM Data                 | 0               |

| 5.46   | Description of Upper Memory Map Tables 03h – 7Fh – Vendor Specific Functions | 0               |

| 5.47   | Description of Upper Memory Map Tables 80h – FFh – Reserved                  | 0               |

|        |                                                                              | 3               |

| Chapte | er 6: Mechanical and Board definition                                        |                 |

| 6.1    | Introduction                                                                 |                 |

|        |                                                                              | 4               |

| 6.2   | XFP D                 | atums and Component Alignment                                                                                                                                                                                                 |                                 |

|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 6.3   | XFP T                 | ransceiver Package Dimensions                                                                                                                                                                                                 |                                 |

| 6.4   | Mating                | of XFP Transceiver PCB to XFP Electrical Connector                                                                                                                                                                            |                                 |

| 6.5   | Host B                | oard Layout                                                                                                                                                                                                                   | 105                             |

| 6.6   | Inserti               | on, Extraction and Retention Forces for XFP Transceivers                                                                                                                                                                      | 106                             |

| 6.7   | Color                 | Coding and Labeling of XFP Transceivers                                                                                                                                                                                       |                                 |

| 6.8   |                       | and EMI Gasket Design for Systems Using XFP Transceivers                                                                                                                                                                      |                                 |

| 6.9   |                       | onnector Mechanical Specifications                                                                                                                                                                                            |                                 |

| 6.10  |                       | age Assembly Dimensions                                                                                                                                                                                                       |                                 |

|       | 6.10.1                | XFP Cage Housing                                                                                                                                                                                                              |                                 |

|       | 6.10.2                | XFP Cage Rear EMI Gaskets                                                                                                                                                                                                     |                                 |

|       |                       | 6.10.2.1XFP Upper Rear EMI Gasket                                                                                                                                                                                             |                                 |

|       |                       | 6.10.2.2Lower Rear EMI Gasket                                                                                                                                                                                                 |                                 |

|       |                       | 6.10.2.3XFP Intermediate Rear Cage EMI Gasket (Finger Stock)                                                                                                                                                                  | 113                             |

|       | 6.10.3                | XFP Cage Front Cage EMI Gasket (Finger Stock)                                                                                                                                                                                 | 113                             |

|       | 6.10.4                | XFP Front Flange                                                                                                                                                                                                              | 114                             |

| 6.11  | XFP H                 | eat Sink Clip Dimensions                                                                                                                                                                                                      | 116                             |

| 6.12  | An Exa                | ample XFP Heat Sink                                                                                                                                                                                                           | 117                             |

| 6.13  | Enviro                | nmental and Thermal                                                                                                                                                                                                           | 118                             |

| 6.14  | Dust/E                | MI Cover                                                                                                                                                                                                                      | 118                             |

| Apper | ndix A:               | Application Reference Model                                                                                                                                                                                                   |                                 |

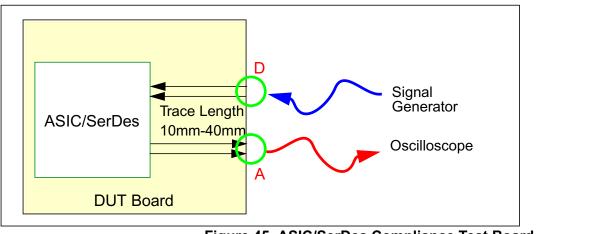

|       | A.1                   | ASIC/SerDes Compliance Testing                                                                                                                                                                                                | 119                             |

|       | A.2                   | Host System Compliance Testing                                                                                                                                                                                                | 120                             |

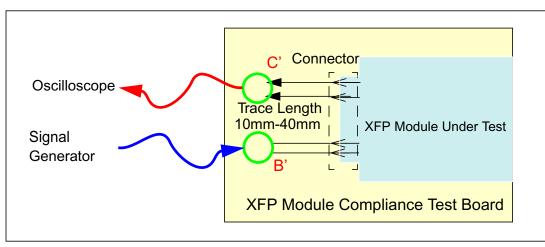

|       | A.3                   | XFP Module Compliance Testing                                                                                                                                                                                                 | 120                             |

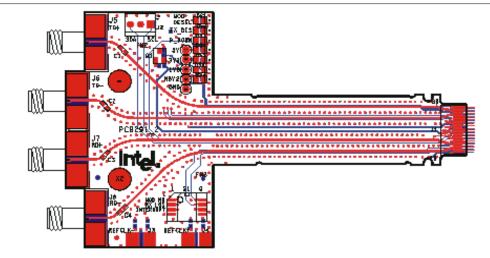

|       | A.4                   | HOST SYSTEM COMPLIANCE TEST BOARD                                                                                                                                                                                             |                                 |

|       |                       | A.4.1 Host System Compliance Board Material and Layer Stack-up                                                                                                                                                                |                                 |

|       |                       | A.4.2 Host System Compliance Test Board Partlist                                                                                                                                                                              |                                 |

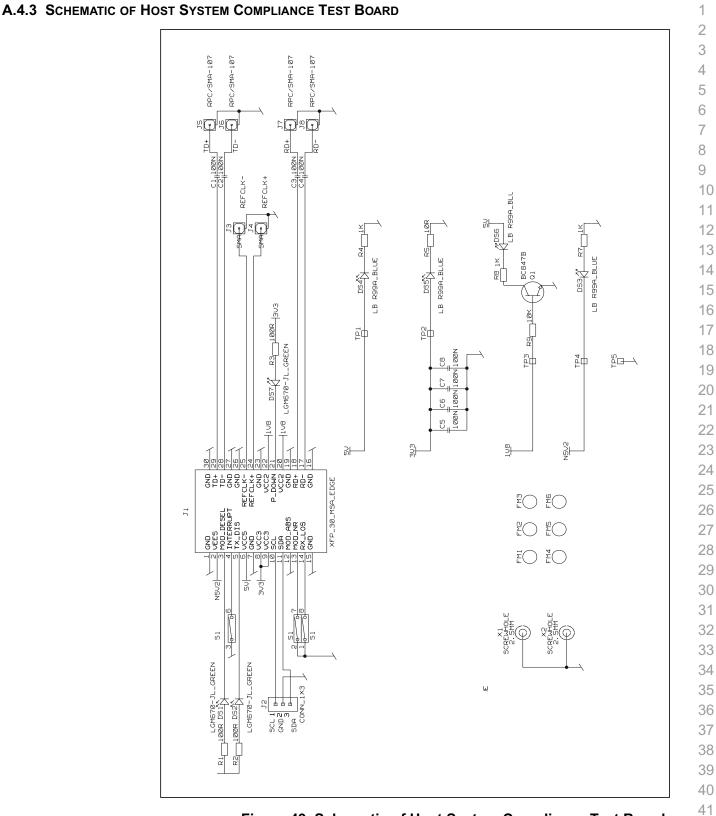

|       |                       | A.4.3 Schematic of Host System Compliance Test Board                                                                                                                                                                          | 124                             |

|       |                       | A.4.4 Gerber file and S parameter measurements                                                                                                                                                                                | 125                             |

|       | A.5                   | XFP MODULE COMPLIANCE TEST BOARD                                                                                                                                                                                              |                                 |

|       |                       |                                                                                                                                                                                                                               |                                 |

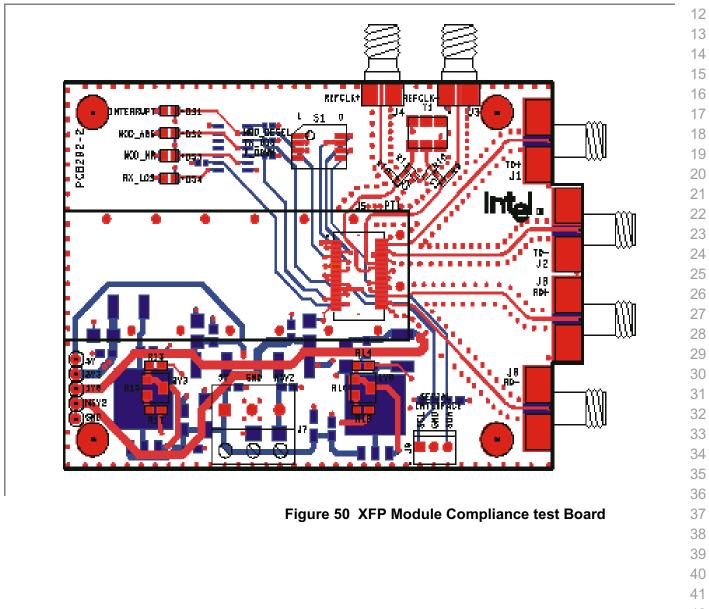

|       |                       | A.5.1 XFP Module Board Material and Layer Stack-up                                                                                                                                                                            | 126                             |

|       |                       | <ul><li>A.5.1 XFP Module Board Material and Layer Stack-up</li><li>A.5.2 XFP Module Compliance Board Partlist</li></ul>                                                                                                       |                                 |

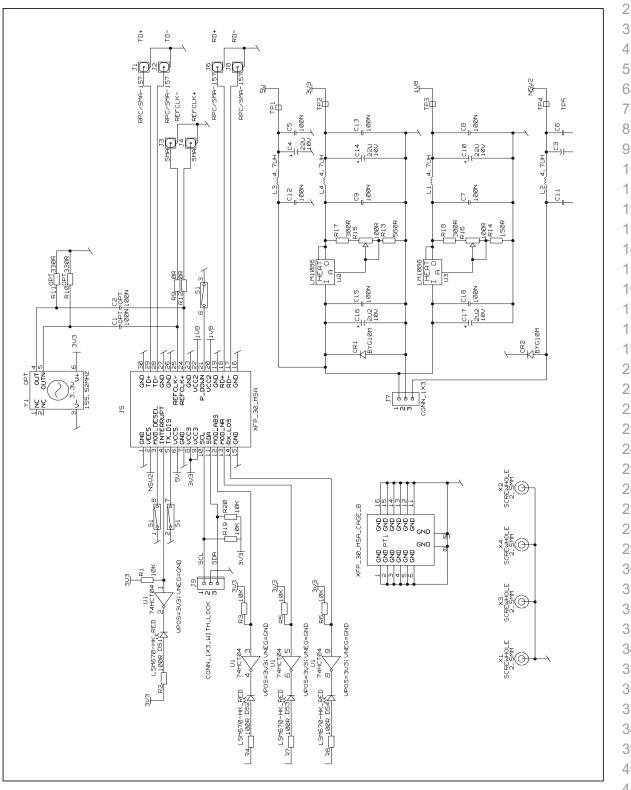

|       |                       |                                                                                                                                                                                                                               | 127                             |

|       |                       | A.5.2 XFP Module Compliance Board Partlist                                                                                                                                                                                    | 127<br>128                      |

| Apper | ndix B:               | <ul><li>A.5.2 XFP Module Compliance Board Partlist</li><li>A.5.3 Schematic of the XFP Compliance Test Board</li></ul>                                                                                                         | 127<br>128<br>129               |

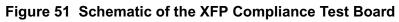

| Apper | <b>ndix B:</b><br>B.1 | <ul> <li>A.5.2 XFP Module Compliance Board Partlist</li> <li>A.5.3 Schematic of the XFP Compliance Test Board</li> <li>A.5.4 Gerber files and Measured S-Parameters</li> <li>XFI Channel Measurements and Modeling</li> </ul> | 127<br>128<br>129<br><b>130</b> |

| Apper | B.1                   | <ul> <li>A.5.2 XFP Module Compliance Board Partlist</li> <li>A.5.3 Schematic of the XFP Compliance Test Board</li> <li>A.5.4 Gerber files and Measured S-Parameters</li> <li>XFI Channel Measurements and Modeling</li></ul>  |                                 |

| Apper |                       | <ul> <li>A.5.2 XFP Module Compliance Board Partlist</li> <li>A.5.3 Schematic of the XFP Compliance Test Board</li> <li>A.5.4 Gerber files and Measured S-Parameters</li> <li>XFI Channel Measurements and Modeling</li> </ul> |                                 |

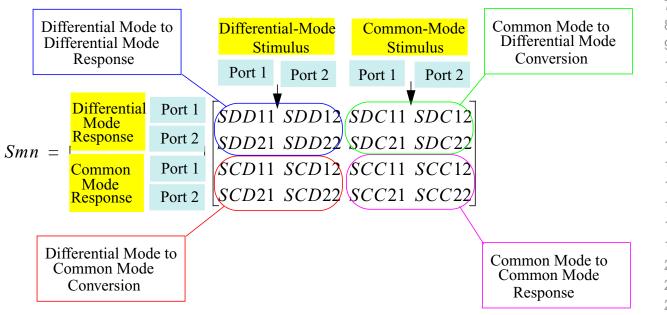

| Appendix C: | Differential S-Parameters and TDR                     | 136 |

|-------------|-------------------------------------------------------|-----|

| C.1         | Choosing S-Parameters vs TDR                          | 136 |

| C.2         | Differential Impedance                                | 137 |

| C.3         | 4 Port Single-Ended S-Parameter Definition            | 138 |

| C.4         | 2 Port Mixed Mode Differential S-Parameter Definition | 138 |

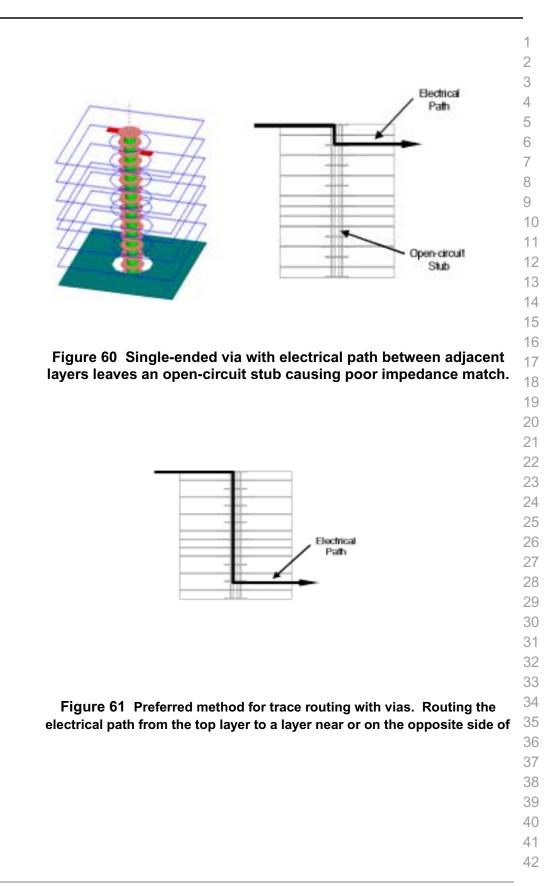

| Appendix D: | Optimum Via Design                                    | 141 |

| D.1         | Vias                                                  | 141 |

| D.2         | Single-ended Vias                                     | 141 |

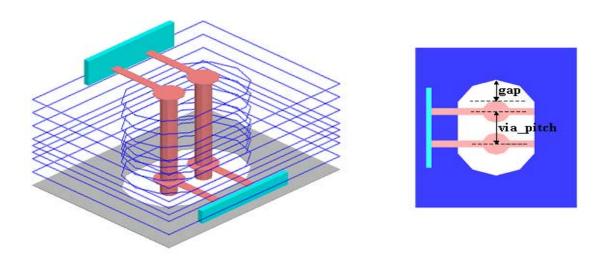

| D.3         | Differential Vias                                     | 143 |

| D.4         | GSSG Differential Vias                                |     |

| Appendix E: | Jitter Methodology and Measurement                    | 148 |

| E.1         | Eye Mask Compliance                                   |     |

| E.2         | Non-DDJ Eye Mask                                      | 150 |

| E.3         | Stress Eye Test for RX Tolerance Testing              |     |

| E.4         | Jitter Peaking Specifications and Measurements        |     |

| E.5         | AC Common Mode Test                                   | 153 |

| E.6         | Termination Mismatch                                  | 153 |

| E.7         | Power supply noise testing methodology                | 155 |

|             | E.7.1 Power Supply Noise compliance                   | 155 |

|             | E.7.2 Power Supply Noise Methodology                  | 155 |

|             | E.7.3 Power Supply Noise Methodology                  | 155 |

| Appendix F: | Module Thermal Testing                                | 157 |

| F.1         | Module Thermal Power Classes                          | 157 |

| F.2         | Thermal Test Recommendation                           | 157 |

| F.3         | Thermal Test Configuration                            | 158 |

|             |                                                       |     |

|             |                                                       |     |

## List of Figures

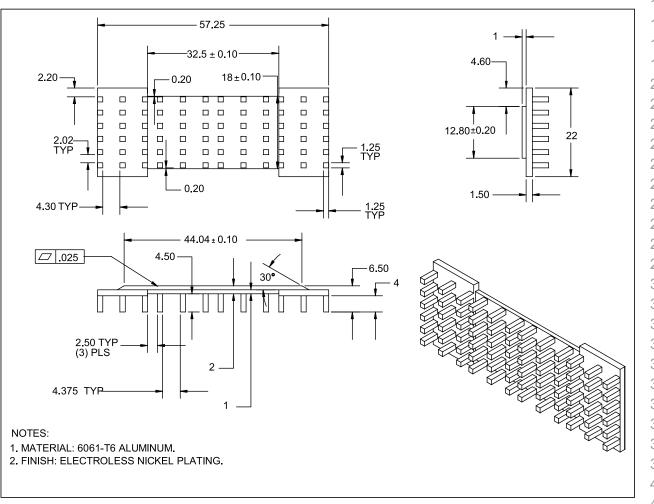

| Figure 1  | Host PCB XFP Pinout Top View                                         |    |

|-----------|----------------------------------------------------------------------|----|

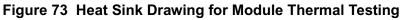

| Figure 2  | Power Noise Requirement                                              |    |

| Figure 3  | Example of Host Board Supply Filtering Network                       |    |

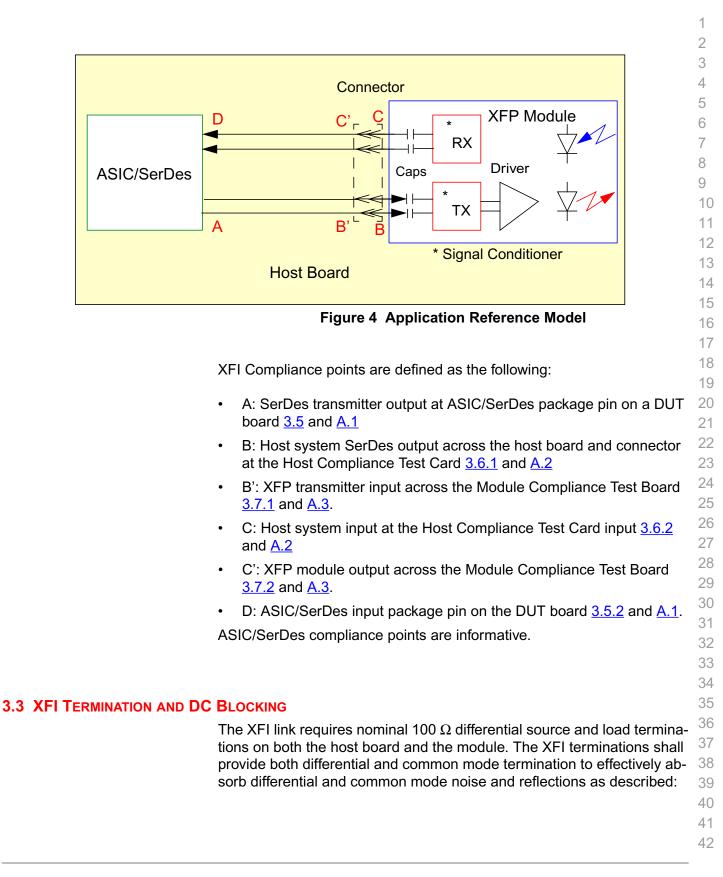

| Figure 4  | Application Reference Model                                          |    |

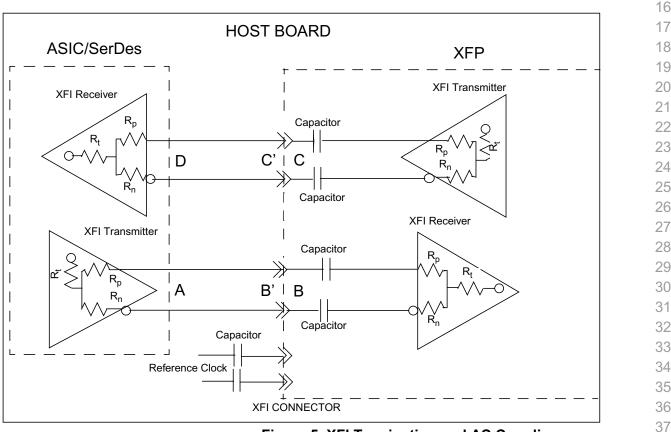

| Figure 5  | XFI Termination and AC Coupling                                      | 18 |

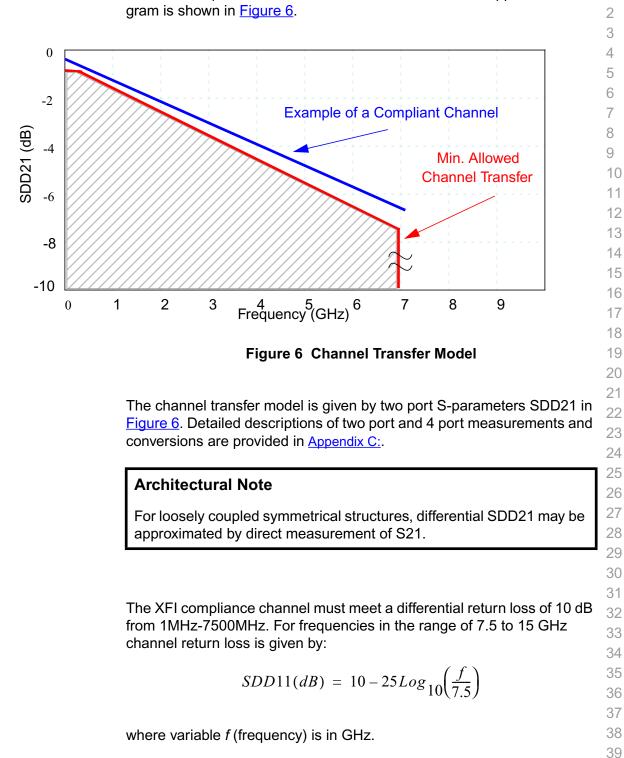

| Figure 6  | Channel Transfer Model                                               |    |

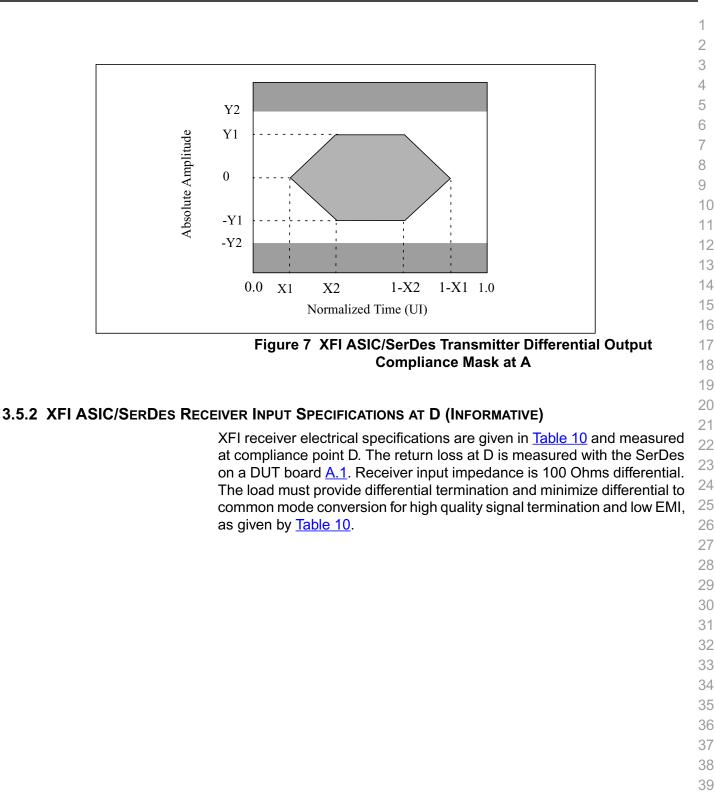

| Figure 7  | XFI ASIC/SerDes Transmitter Differential Output Compliance Mask at A | 23 |

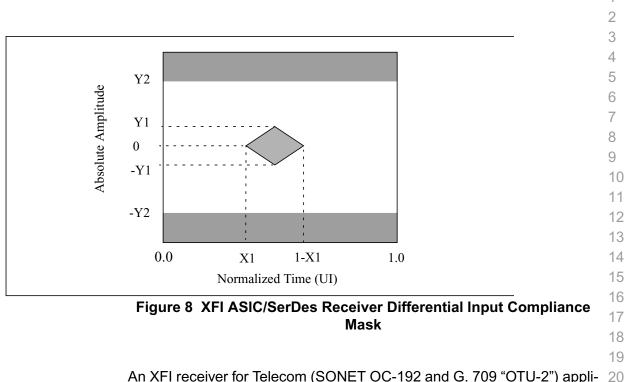

| Figure 8  | XFI ASIC/SerDes Receiver Differential Input Compliance Mask          | 25 |

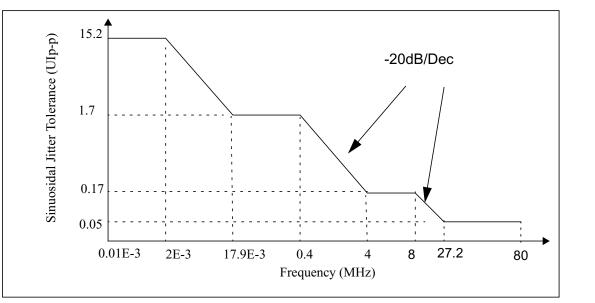

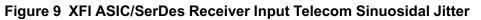

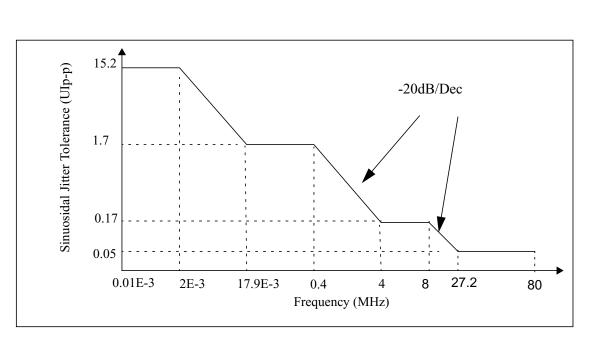

| Figure 9  | XFI ASIC/SerDes Receiver Input Telecom Sinuosidal Jitter Tolerance   | 25 |

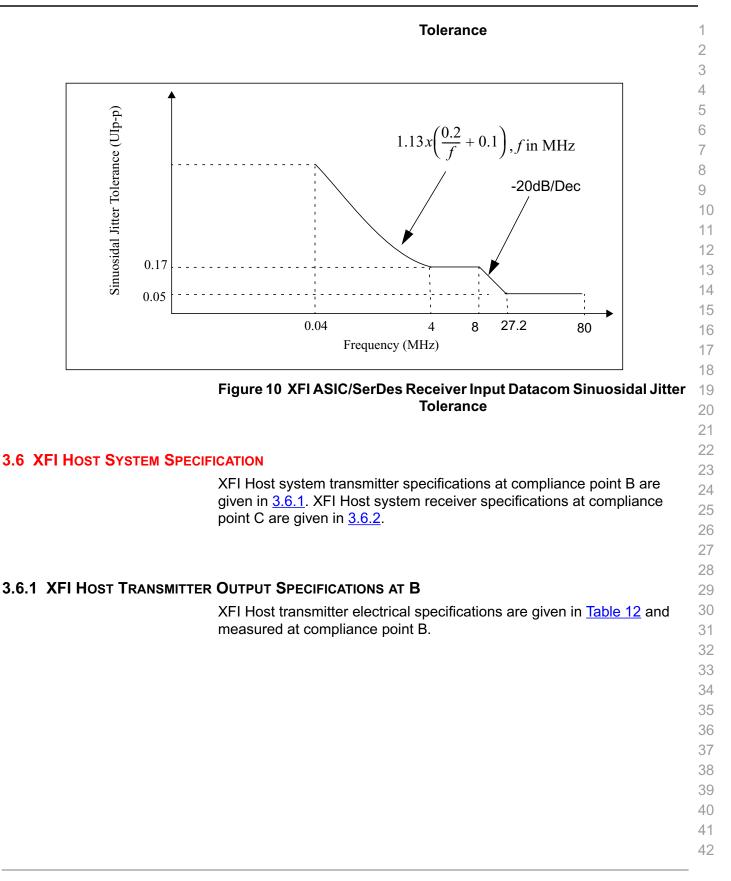

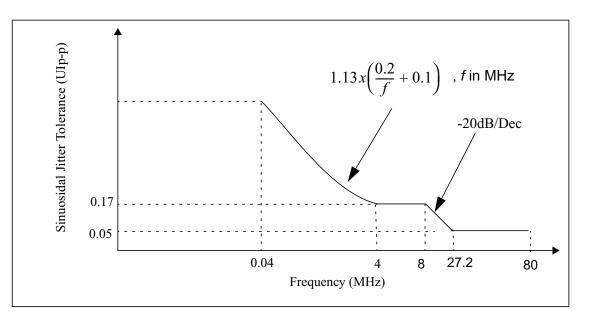

| Figure 10 | XFI ASIC/SerDes Receiver Input Datacom Sinuosidal Jitter Tolerance   | 26 |

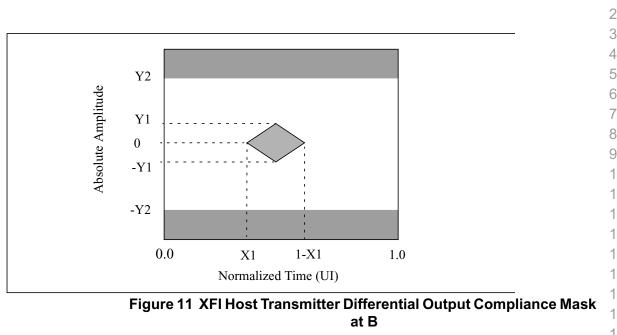

| Figure 11 | XFI Host Transmitter Differential Output Compliance Mask at B        | 28 |

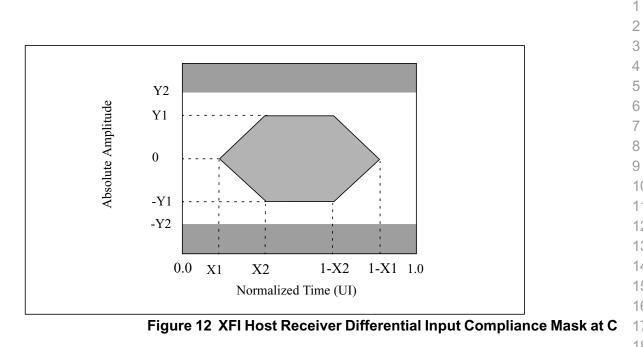

| Figure 12 | XFI Host Receiver Differential Input Compliance Mask at C            | 30 |

| Figure 13 | XFI Host Receiver Telecom Input Sinuosidal Jitter Tolerance          | 31 |

| Figure 14 | XFI Host Receiver Input Datacom Sinuosidal Jitter Tolerance          | 31 |

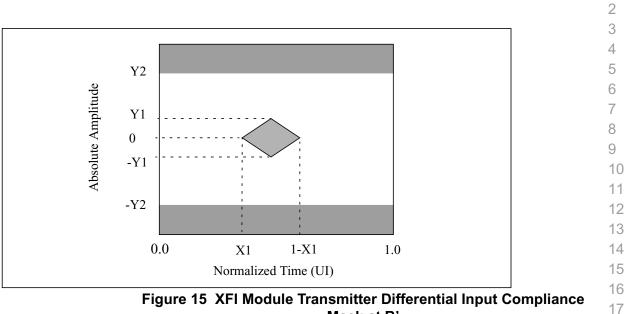

| Figure 15 | XFI Module Transmitter Differential Input Compliance Mask at B'      | 34 |

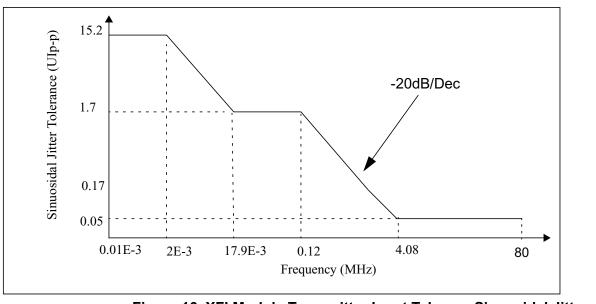

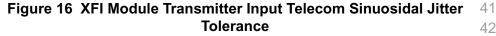

| Figure 16 | XFI Module Transmitter Input Telecom Sinuosidal Jitter Tolerance     | 34 |

| Figure 17 | XFI Module Transmitter Input Datacom Margin Mask                     | 35 |

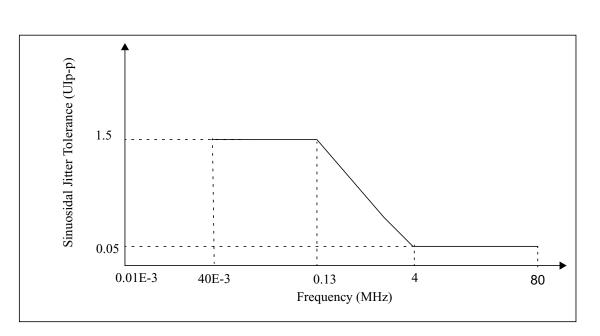

| Figure 18 | XFI Module Receiver Differential Output Compliance Mask at C'        |    |

| Figure 19 | XFP Timing Diagram                                                   |    |

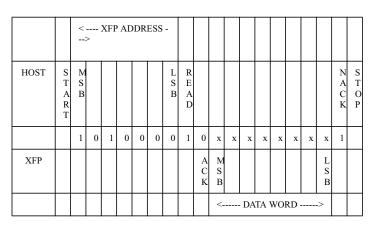

| Figure 20 | XFP Current Address Read Operation                                   |    |

| Figure 21 | XFP Random Read                                                      |    |

| Figure 22 | Sequential Address Read Starting at XFP Current Address              |    |

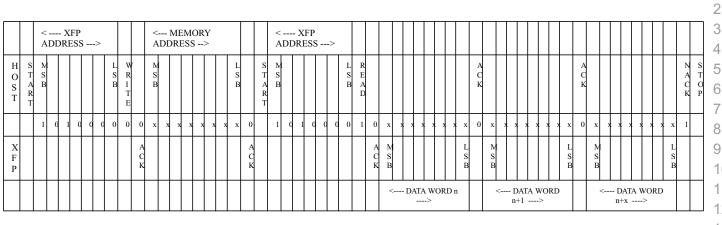

| Figure 23 | Sequential Address Read Starting with Random XFP Read                |    |

| Figure 24 | XFP Read Operation Packet Error Checking                             |    |

| Figure 25 | XFP Write Byte Operation                                             |    |

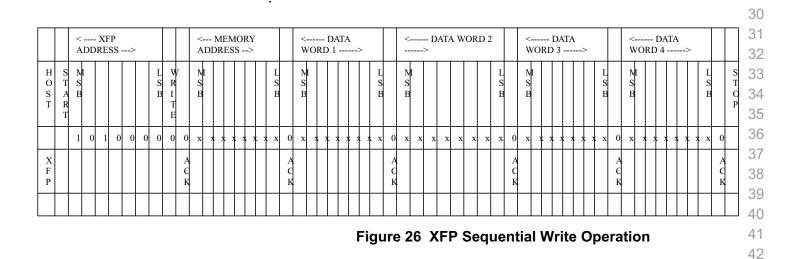

| Figure 26 | XFP Sequential Write Operation                                       |    |

| Figure 27 | XFP Write Operation Packet Error Checking                            |    |

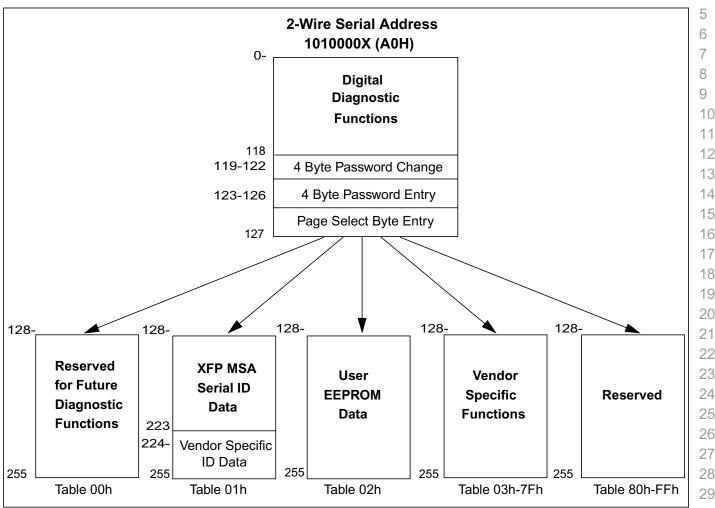

| Figure 28 | 2-wire Serial Digital Diagnostic Memory Map                          |    |

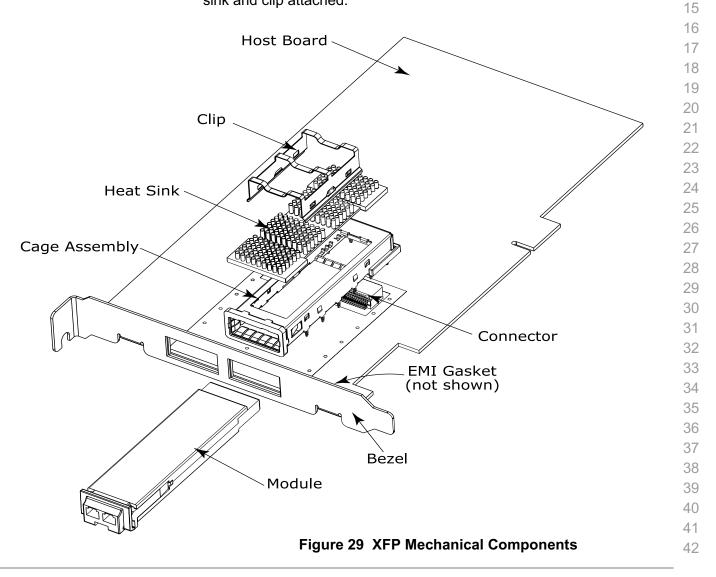

| Figure 29 | XFP Mechanical Components                                            |    |

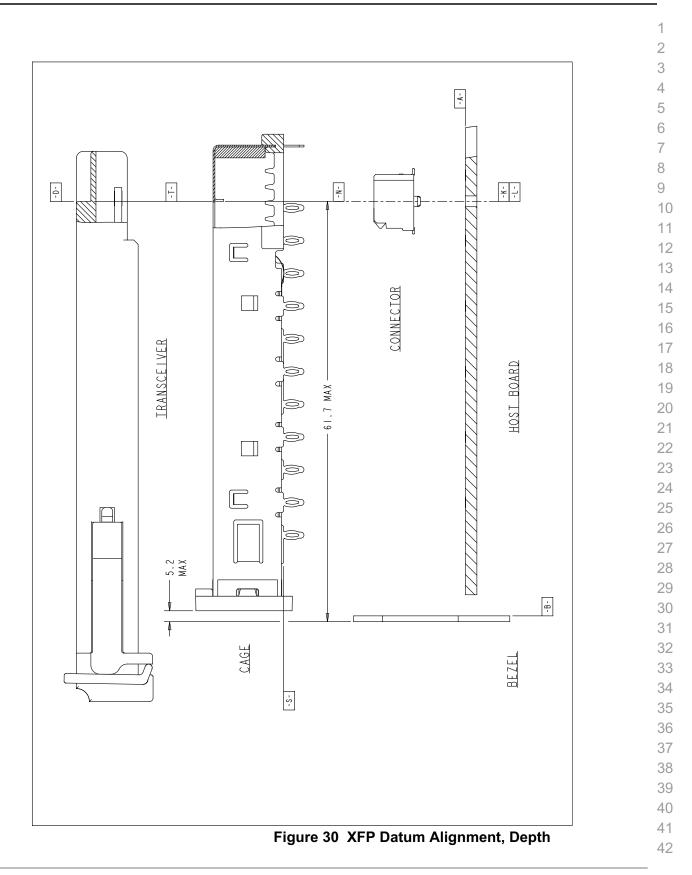

| Figure 30 | XFP Datum Alignment, Depth                                           | 99 |

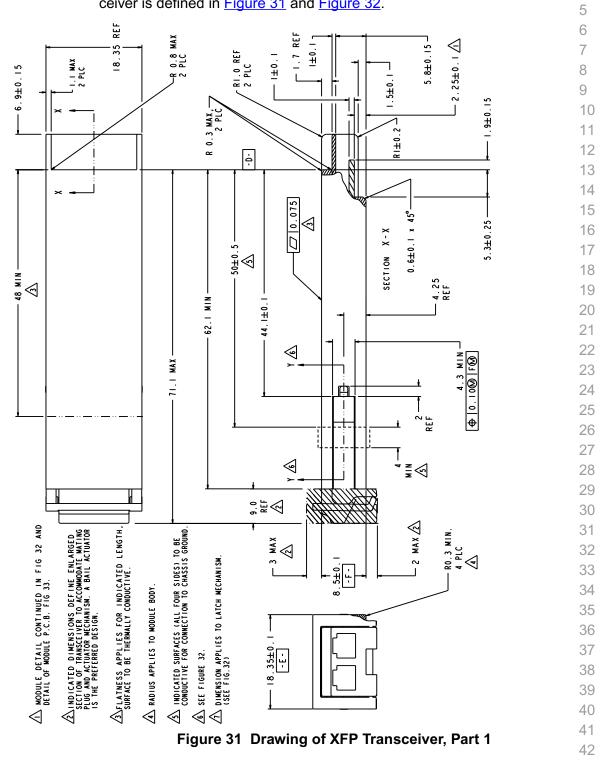

| Figure 31 | Drawing of XFP Transceiver, Part 1                                   |    |

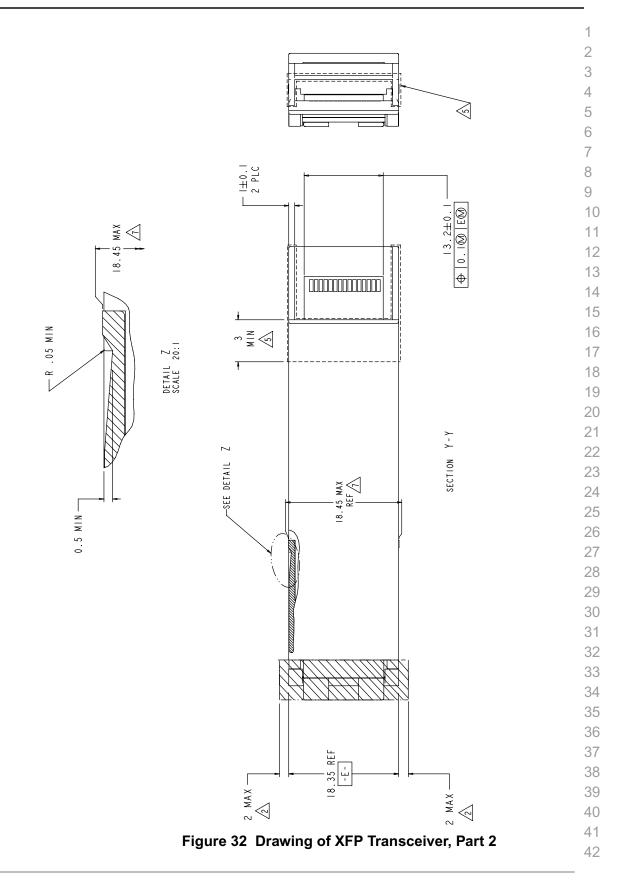

| Figure 32 | Drawing of XFP Transceiver, Part 2                                   |    |

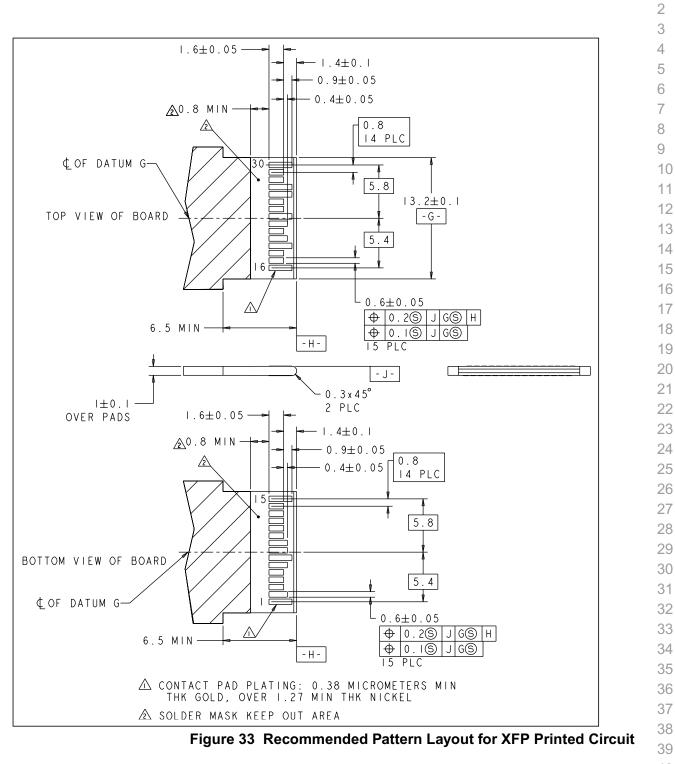

| Figure 33 | Recommended Pattern Layout for XFP Printed Circuit                   |    |

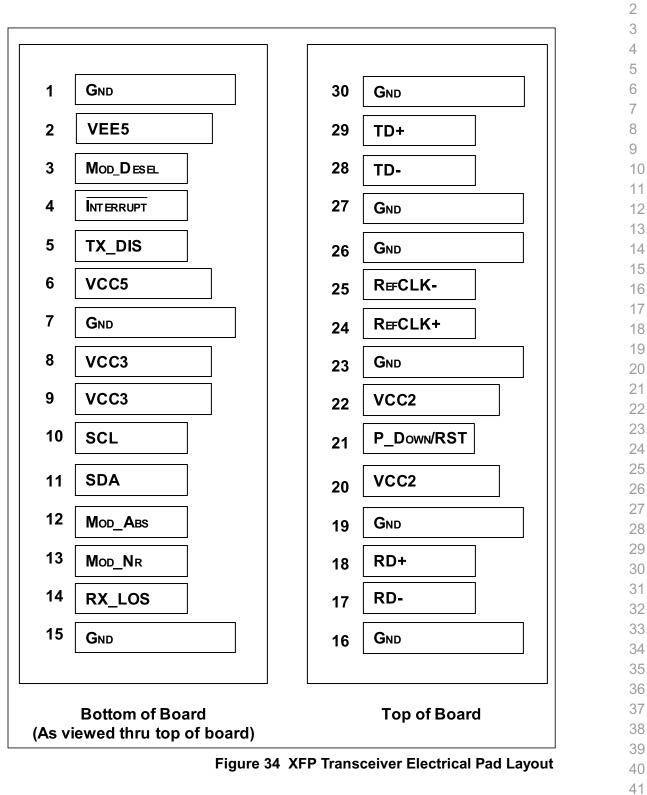

| Figure 34 | XFP Transceiver Electrical Pad Layout                                |    |

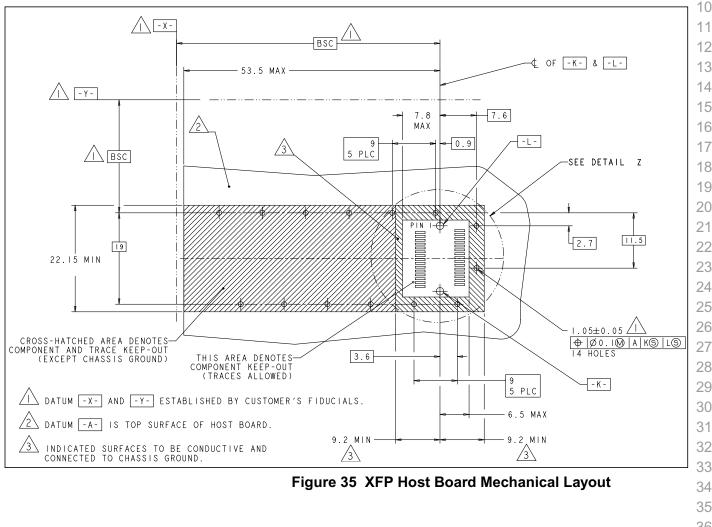

| Figure 35 | XFP Host Board Mechanical Layout                                     |    |

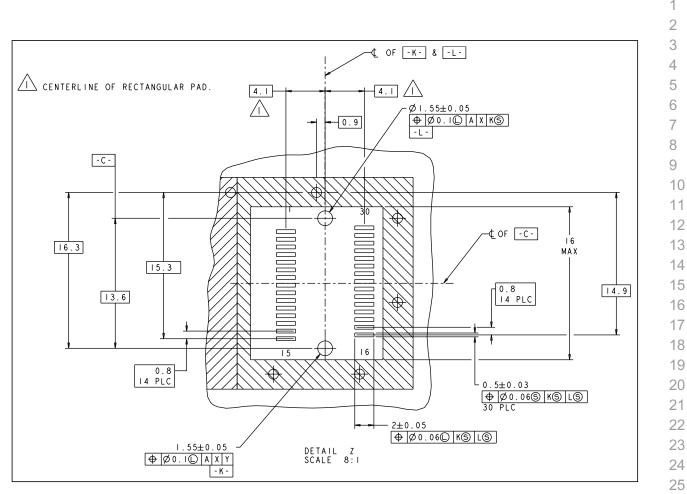

| Figure 36 | XFP Detail Host Board Mechanical Layout, Detail Z                    |    |

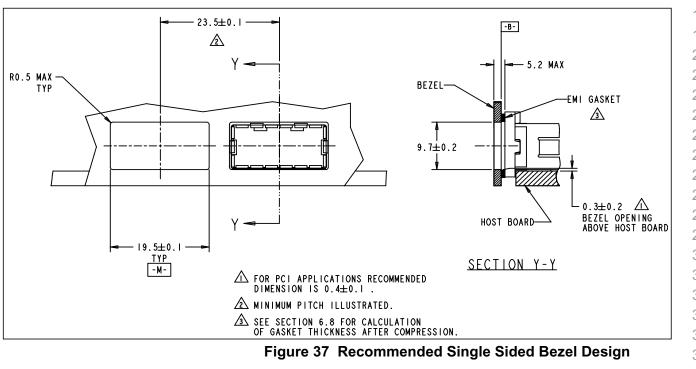

| Figure 37 | Recommended Single Sided Bezel Design                                |    |

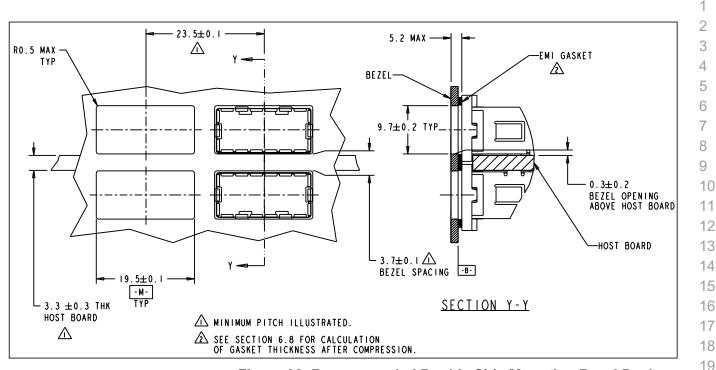

| Figure 38 | Recommended Double Side Mounting Bezel Design                        |    |

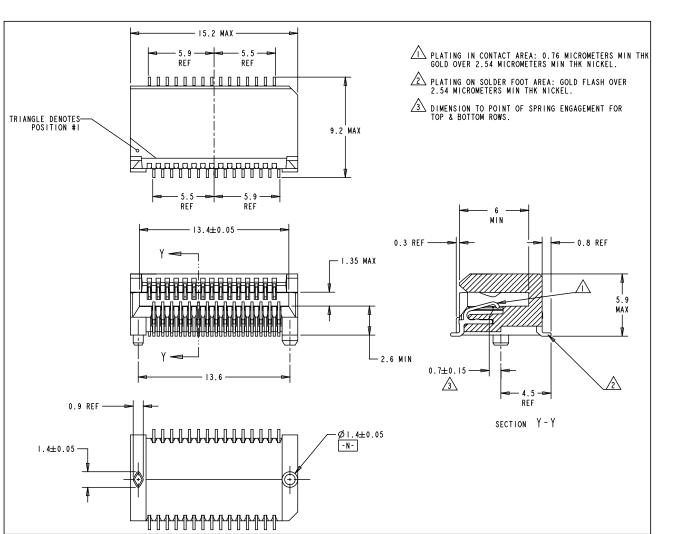

| Figure 39 | XFP Transceiver Connector Illustration                               |    |

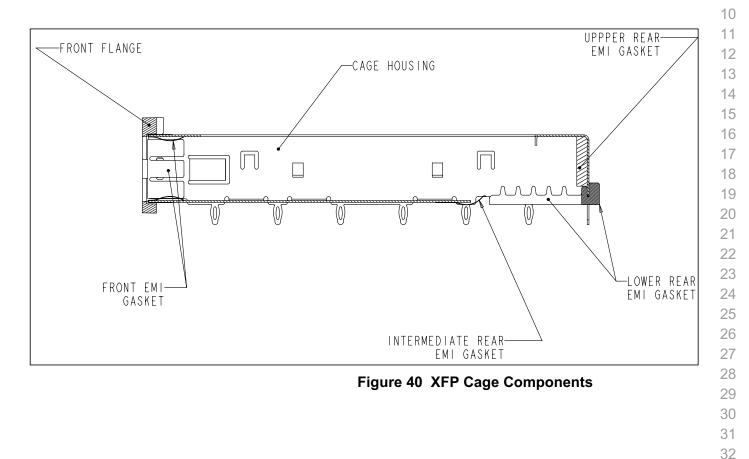

| Figure 40 | XFP Cage Components                                                  |    |

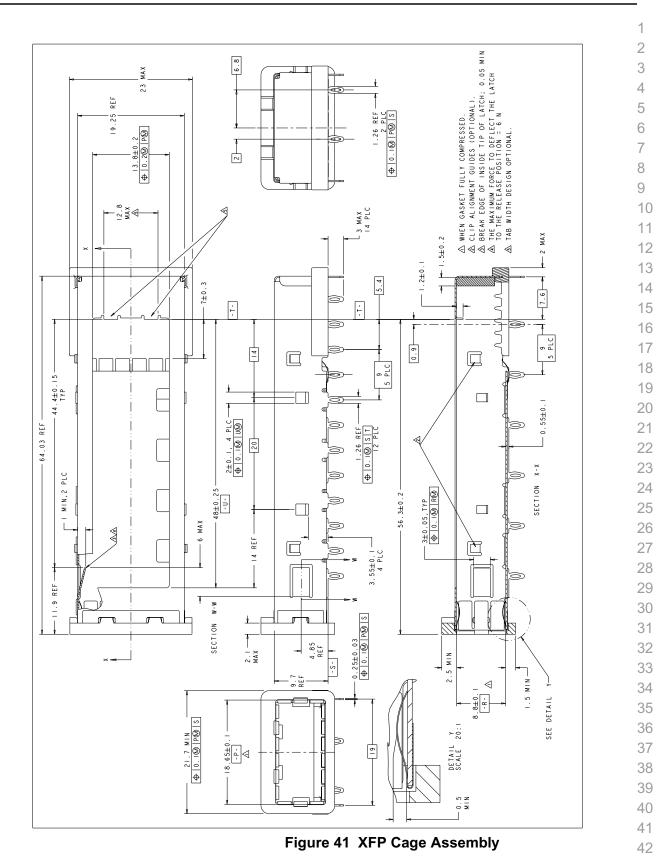

| Figure 41 | XFP Cage Assembly                                                    |    |

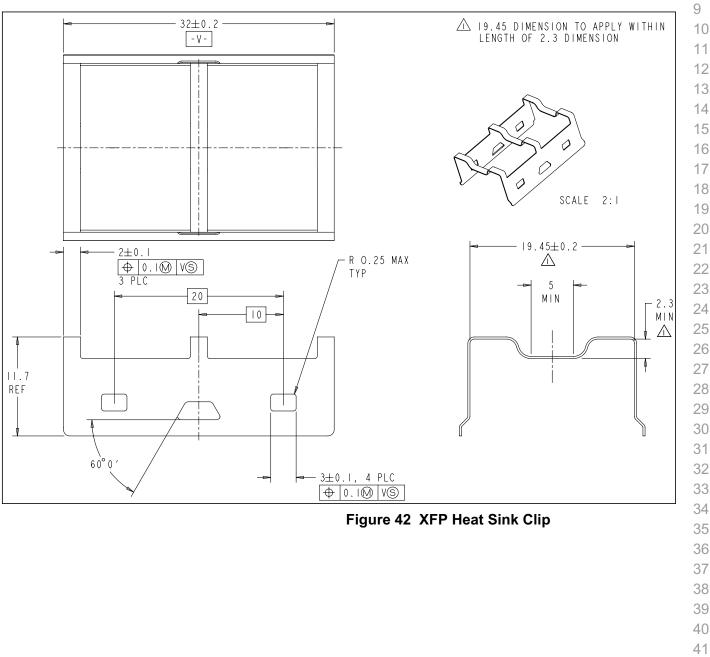

| Figure 42                           | XFP Heat Sink Clip                                                                     | 116               |

|-------------------------------------|----------------------------------------------------------------------------------------|-------------------|

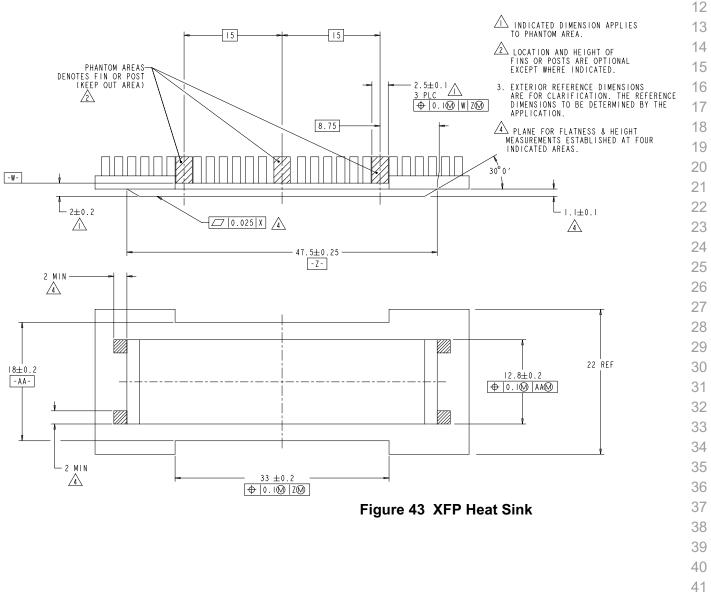

| Figure 43                           | XFP Heat Sink                                                                          |                   |

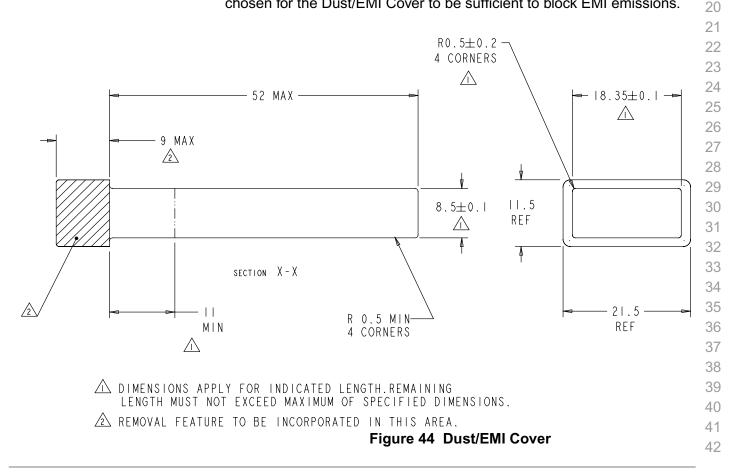

| Figure 44                           | Dust/EMI Cover                                                                         | 118               |

| Figure 45                           | ASIC/SerDes Compliance Test Board                                                      |                   |

| Figure 46                           | Host System Compliance Test Diagram                                                    |                   |

| Figure 47                           | XFP Module Compliance Test Diagram                                                     |                   |

| Figure 48                           | Host System compliance Test Board                                                      |                   |

| Figure 49                           | Schematic of Host System Compliance Test Board                                         | 124               |

| Figure 50                           | XFP Module Compliance test Board                                                       |                   |

| Figure 51                           | Schematic of the XFP Compliance Test Board                                             |                   |

| Figure 52                           | XFI Electrical Channel Definition                                                      | 130               |

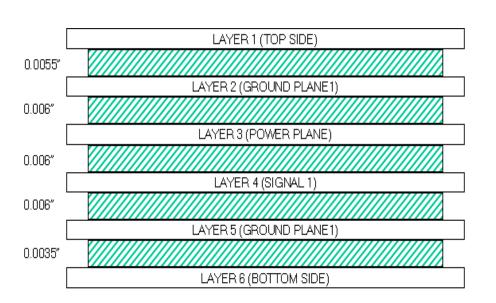

| Figure 53                           | PCB Board Stack up                                                                     | 131               |

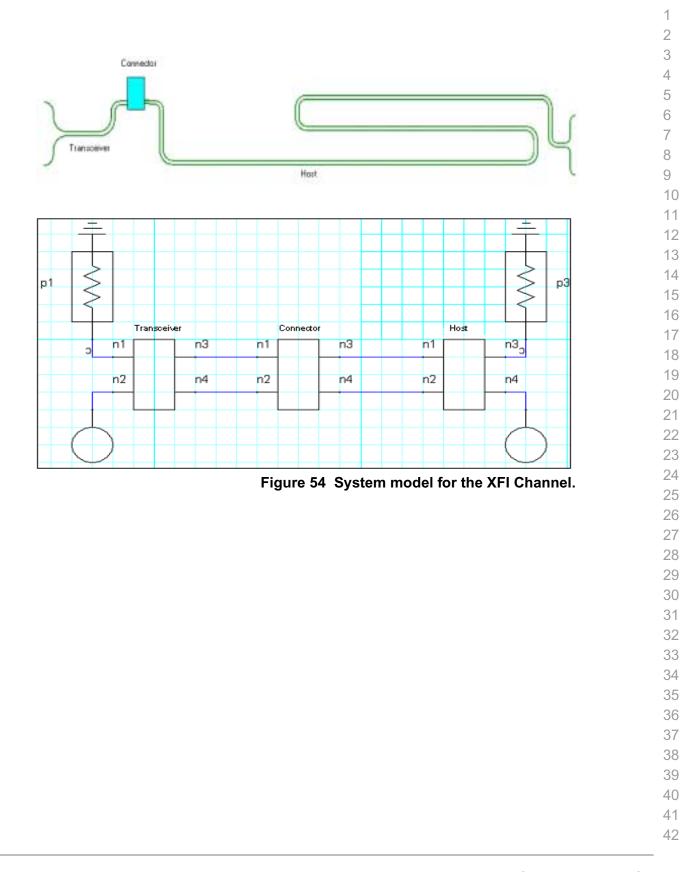

| Figure 54                           | System model for the XFI Channel.                                                      | 133               |

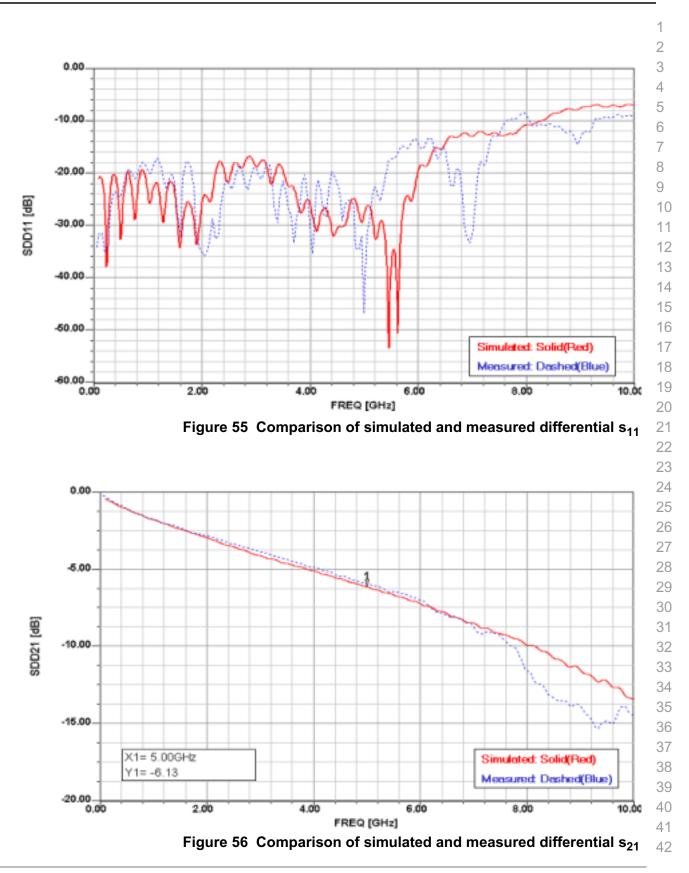

| Figure 55                           | Comparison of simulated and measured differential s11                                  | 134               |

| Figure 56                           | Comparison of simulated and measured differential s21                                  |                   |

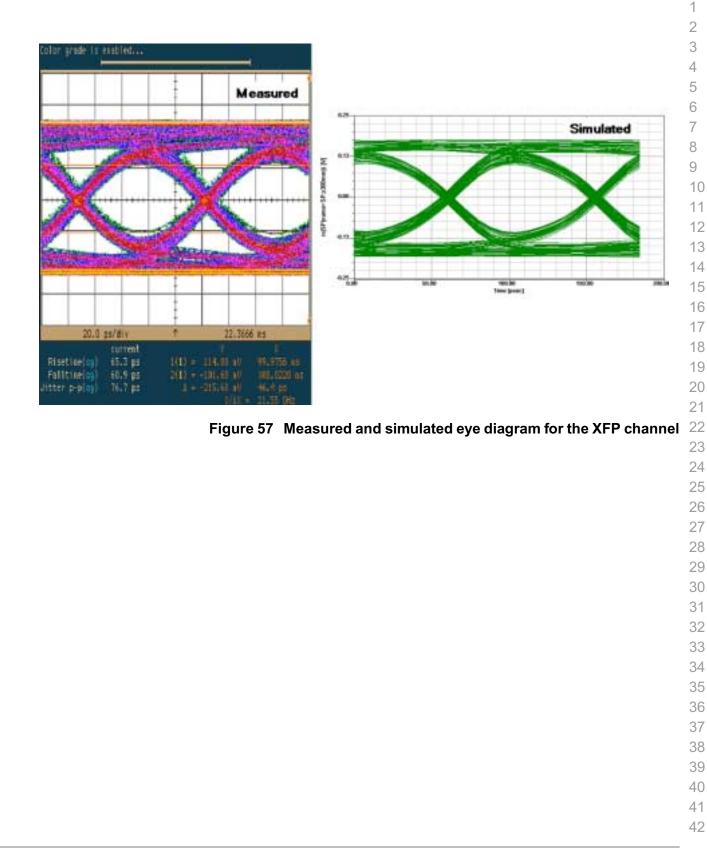

| Figure 57                           | Measured and simulated eye diagram for the XFP channel                                 | 135               |

| Figure 58                           | 4 Port DUT                                                                             |                   |

| Figure 59                           | Differential 2 Port DUT                                                                | 138               |

| Figure 60                           | Single-ended via with electrical path between adjacent layers leaves an open-circuit   |                   |

| -                                   | causing poor impedance match                                                           | 142               |

| Figure 61                           | Preferred method for trace routing with vias. Routing the electrical path from the to  | p laye            |

|                                     | to a layer near or on the opposite side of the board minimizes the open-circuited stub | 142               |

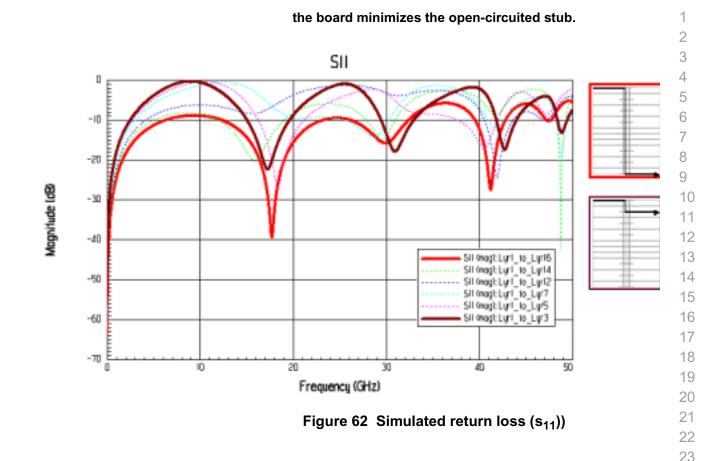

| Figure 62                           | Simulated return loss (s11))                                                           | 143               |

| Figure 63                           | Differential via geometry a 100mil multilayer PCB                                      | 144               |

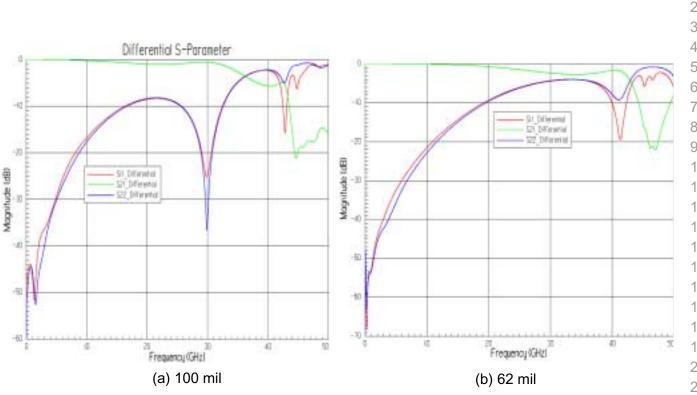

| Figure 64                           | S-parameters for optimized via structures with dimensions given in Table 1. (a) 100 m  |                   |

| -                                   | PCB. (B.) 62 mil thick board.                                                          | 145               |

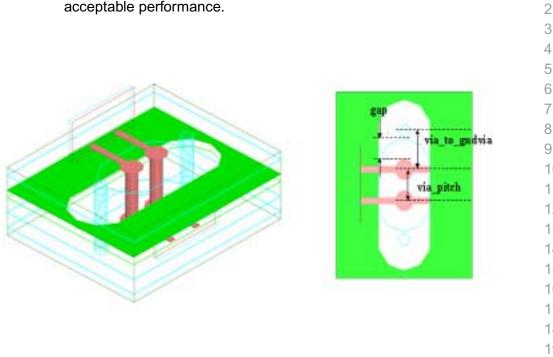

| Figure 65                           | GSSG via structure                                                                     | 146               |

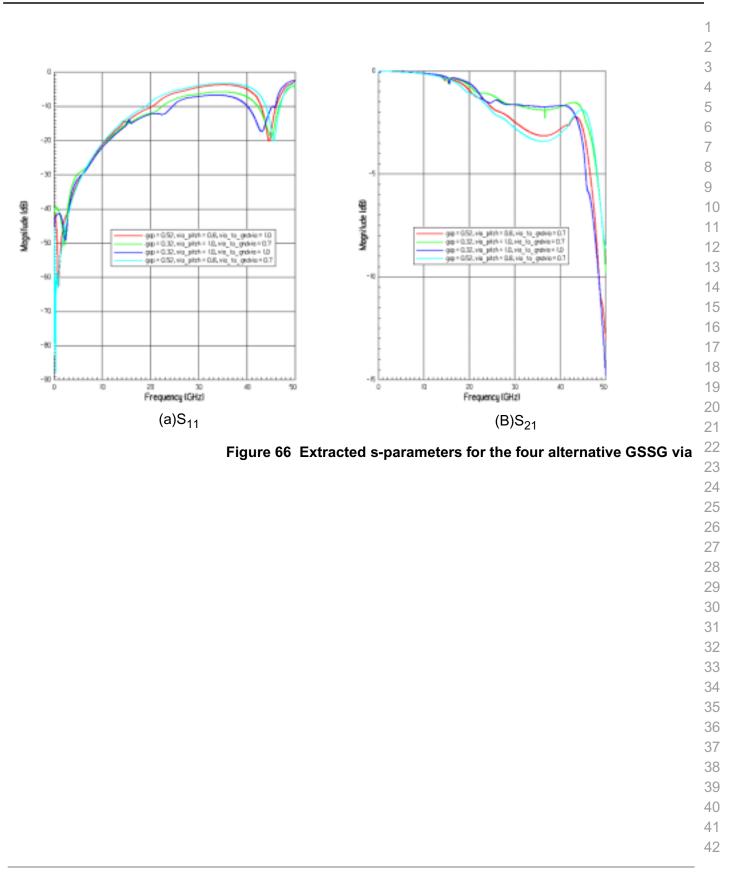

| Figure 66                           | Extracted s-parameters for the four alternative GSSG via                               | 147               |

| Figure 67                           | Eye Template Alignment                                                                 | 149               |

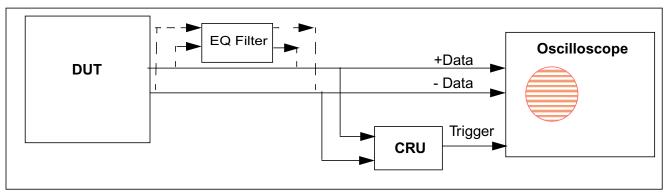

| Figure 68                           | Eye mask measurement setup - block diagram                                             |                   |

| i iguie uo                          |                                                                                        | 150               |

| Figure 69                           | Eye mask measurement setup - block diagram                                             | 130               |

| -                                   | Eye mask measurement setup - block diagram<br>AC Termination Mismatch Measurement      |                   |

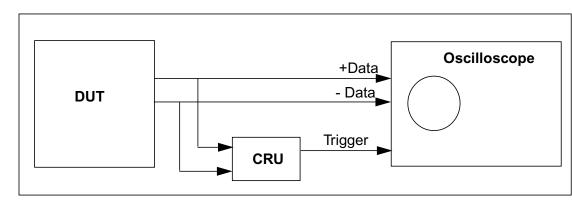

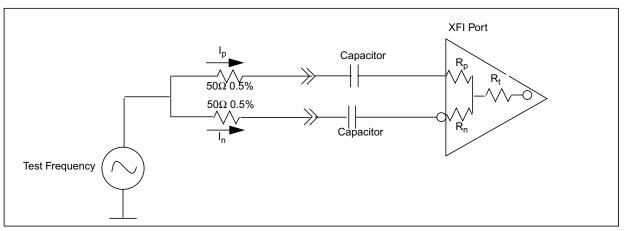

| Figure 69                           | AC Termination Mismatch Measurement                                                    | 154               |

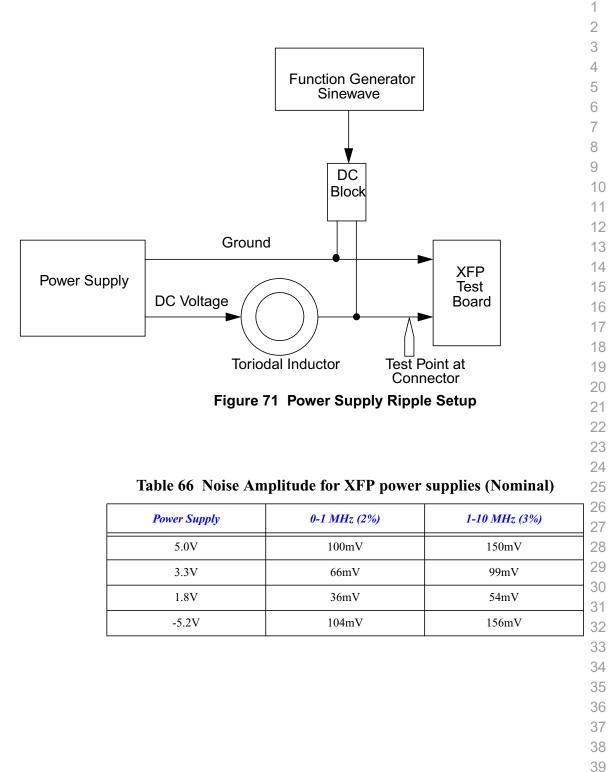

| Figure 69<br>Figure 70              | AC Termination Mismatch Measurement<br>Power Supply Ripple Setup                       | 154<br>156        |

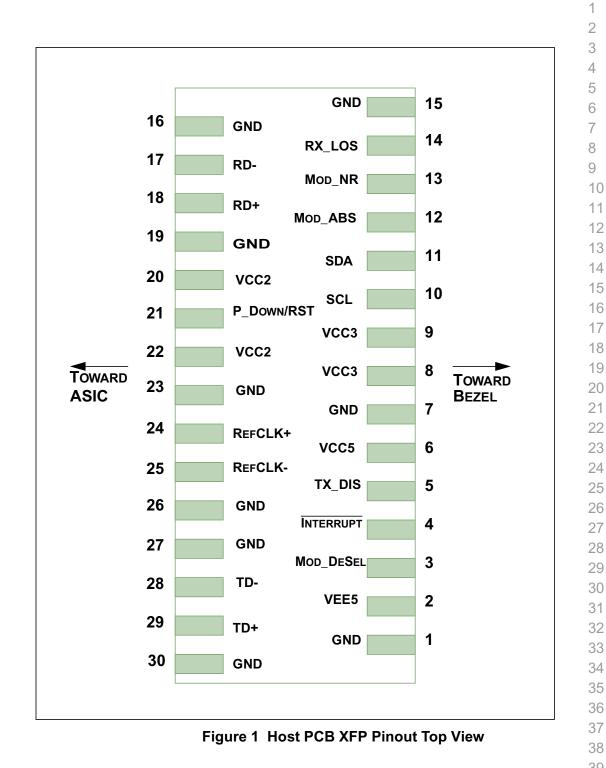

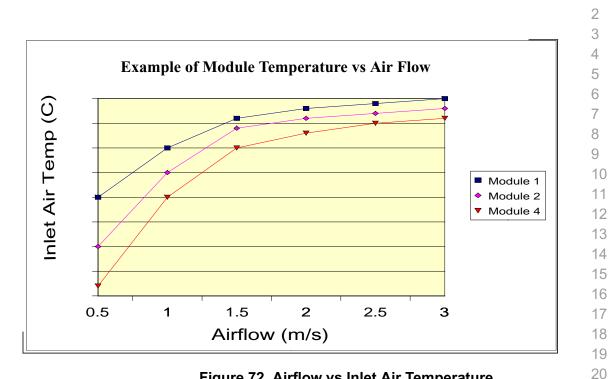

| Figure 69<br>Figure 70<br>Figure 71 | AC Termination Mismatch Measurement                                                    | 154<br>156<br>159 |

### **List of Tables**

| Table 1  | Module Electrical Pin Definition                                  | 5  |

|----------|-------------------------------------------------------------------|----|

| Table 2  | Low speed control and sense signals, electronic characteristics   | 9  |

| Table 3  | Timing Parameters for XFP Management                              | 10 |

| Table 4  | XFP Power Supply                                                  | 14 |

| Table 5  | XFI Supported Data Rates                                          | 16 |

| Table 6  | XFI Loss Budget                                                   | 19 |

| Table 7  | Host Board Configuration                                          | 21 |

| Table 8  | XFI ASIC/SerDes Transmitter Output Electrical Specifications at A | 22 |

| Table 9  | XFI ASIC/SerDes Transmitter Output Jitter Specifications at A     | 22 |

| Table 10 | XFI ASIC/SerDes Receiver Electrical Input Specifications at D     | 24 |

| Table 11 | XFI ASIC/SerDes Receiver Input Jitter Specifications at D         | 24 |

| Table 12 | XFI Host Transmitter Output Electrical Specifications at B        |    |

| Table 13 | XFI Host Transmitter Output Jitter Specifications at B            | 27 |

| Table 14 | XFI Host Receiver Input Electrical Specifications at C            |    |

| Table 15 | XFI Host Receiver Input Jitter Specifications at C                |    |

| Table 16 | XFI Module Transmitter Input Electrical Specifications at B'      |    |

| Table 17 | XFI Module Transmitter Input Jitter Specifications at B'          |    |

| Table 18 | XFI Module Receiver Output Electrical Specifications at C'        | 36 |

| Table 19 | XFI Module Receiver Output Jitter Specifications at C'            | 36 |

| Table 20 | XFP Telecom Module Transmitter Requirement                        |    |

| Table 21 | XFP Telecom Module Receiver Requirement                           |    |

| Table 22 | XFP Datacom Module Transmitter Requirement                        |    |

| Table 23 | XFP Datacom Module Receiver Requirement                           |    |

| Table 24 | Reference Clock Specifications                                    | 4( |

| Table 25 | Optional Reference Clock Specifications                           | 41 |

| Table 26 | XFP 2-Wire Timing Specifications                                  | 43 |

| Table 27 | XFP Memory Specifications                                         | 44 |

| Table 28 | Single Byte Writable Memory Blocks                                |    |

| Table 29 | Multiple Byte Writable Memory Blocks                              | 44 |

| Table 30 | XFP Device Address                                                | 46 |

| Table 31 | Lower Memory Map                                                  | 57 |

| Table 32 | Identifier values Byte 128                                        | 58 |

| Table 33 | VPS Fields                                                        |    |

| Table 34 | Signal Conditioner Control Field                                  | 70 |

| Table 35 | Alarm and Warning Thresholds                                      | 71 |

| Table 36 | BER Control Fields                                                |    |

| Table 37 | Wavelength Control Fields                                            |      |

|----------|----------------------------------------------------------------------|------|

| Table 38 | FEC Control Fields                                                   |      |

| Table 39 | Latched Interrupt Flag Fields                                        |      |

| Table 40 | Interrupt Masking Bits                                               |      |

| Table 41 | A/D Values                                                           | _    |

| Table 42 | General Control/Status Bits                                          | 6    |

| Table 43 | Packet Error Checking                                                |      |

| Table 44 | Password and Table Select Entry Bytes                                |      |

| Table 45 | I/O Timing for Soft Control & Status Functions                       | 70 9 |

| Table 46 | Serial ID: Data Fields - Page 01h                                    |      |

| Table 47 | Extended Identifier values Byte 129                                  |      |

| Table 48 | Connector values Byte 130                                            | 1    |

| Table 49 | Transceiver codes                                                    |      |

| Table 50 | Encoding Support Byte 139                                            |      |

| Table 51 | Device Technology (Value of lower 4 bits of Byte 147)                |      |

| Table 52 | Transmitter Technology (Value of top 4 bits of Byte 147)             |      |

| Table 53 | CDR Support Byte 164                                                 |      |

| Table 54 | Power Supply Related Fields                                          |      |

| Table 55 | Date Code                                                            |      |

| Table 56 | Diagnostic Monitoring Type                                           |      |

| Table 57 | Enhanced Options                                                     |      |

| Table 58 | Auxiliary A/D Types Byte 222                                         |      |

| Table 59 | Auxiliary Input Types                                                |      |

| Table 60 | Definition of Datums                                                 |      |

| Table 61 | Insertion, Extraction, and Retention Forces                          |      |

| Table 62 | Host System Compliance Test Board Part List                          |      |

| Table 63 | XFP Module Compliance Test Board Part List                           |      |

| Table 64 | Optimized differential via geometry for 100 mil and 62 mil thick PCB |      |

| Table 65 | Four alternative GSSG via dimension                                  |      |

| Table 66 | Noise Amplitude for XFP power supplies (Nominal)                     |      |

| Table 67 | Environmental Test Conditions                                        |      |

|          |                                                                      | 3    |

|          |                                                                      | 3    |

|          |                                                                      | 3    |

### CHAPTER 1: SCOPE OF XFP SPECIFICATION

#### **1.1 INTRODUCTION**

| <ul> <li>This specification defines the electrical, management, and mechan terfaces of the XFP module. The module is a hot pluggable small for serial-to-serial data-agnostic multirate optical transceiver, intended support Telecom (SONET OC-192 and G.709 "OTU-2") and Datace plications (10 Gb/s Ethernet and 10 Gb/s Fibre Channel). Nominal rates range from 9.95 Gb/s, 10.31 Gb/s, 10.52 Gb/s, 10.70 Gb/s, at emerging 11.09 Gb/s. The modules support all data encodings for technologies. The modules may be used to implement single mode multi-mode serial optical interfaces at 850 nm, 1310 nm, or 1550 nm XFP module design may use one of several different optical connets.</li> <li>The XFP specification includes the following information:</li> <li>XFP reference model and description 3.2</li> <li>Chapter 2: XFP Electrical Interface, Low Speed Electrical Interface Gb/s serial electrical specification (XFI)</li> <li>Chapter 3: High Speed Electrical Specification XFL, High spee Gb/s serial electrical specification (XFI)</li> <li>Chapter 5: Management interface, Management and diagnost terface</li> <li>Chapter 6: Mechanical and Board definition, Mechanical interincluding guides, EMI shields, module retention, cooling, and e cal connector.</li> <li>Appendix A: Application Reference Model</li> <li>Appendix A: Application Reference Model</li> <li>Appendix B: XFI Channel Measurements and Modeling.</li> <li>Appendix C: Differential S-Parameters and TDR.</li> <li>Appendix D: Optimum Via Design.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| <ul> <li>terfaces of the XFP module. The module is a hot pluggable small for serial-to-serial data-agnostic multirate optical transceiver, intended support Telecom (SONET OC-192 and G.709 "OTU-2") and Datace plications (10 Gb/s Ethernet and 10 Gb/s Fibre Channel). Nominal rates range from 9.95 Gb/s, 10.31 Gb/s, 10.52 Gb/s, 10.70 Gb/s, and emerging 11.09 Gb/s. The modules support all data encodings for technologies. The modules may be used to implement single modumulti-mode serial optical interfaces at 850 nm, 1310 nm, or 1550 nm XFP module design may use one of several different optical connet 5.17. An adaptable heatsink option allows a single module design compatible with a variety of hosts.</li> <li>The XFP specification includes the following information:</li> <li>XFP reference model and description 3.2</li> <li>Chapter 2: XFP Electrical Interface, Low Speed Electrical Interface following information:</li> <li>XFP reference model and description (XFI)</li> <li>Chapter 4: XFP 2-Wire Interface Protocol., XFP 2-Wire Interface following guides, EMI shields, module retention, cooling, and e cal connector.</li> <li>Appendix A: Application Reference Model</li> <li>Appendix B: XFI Channel Measurements and Modeling.</li> <li>Appendix C: Differential S-Parameters and TDR.</li> <li>Appendix D: Optimum Via Design.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | nical ir |

| <ul> <li>support Telecom (SONET OC-192 and G.709 "OTU-2") and Datace plications (10 Gb/s Ethernet and 10 Gb/s Fibre Channel). Nominal rates range from 9.95 Gb/s, 10.31 Gb/s, 10.52 Gb/s, 10.70 Gb/s, at emerging 11.09 Gb/s. The modules support all data encodings for technologies. The modules may be used to implement single mode multi-mode serial optical interfaces at 850 nm, 1310 nm, or 1550 nm XFP module design may use one of several different optical connets. An adaptable heatsink option allows a single module design compatible with a variety of hosts.</li> <li>The XFP specification includes the following information:</li> <li>XFP reference model and description 3.2</li> <li>Chapter 2: XFP Electrical Interface , Low Speed Electrical Interface Gb/s serial electrical specification (XFI)</li> <li>Chapter 4: XFP 2-Wire Interface Protocol , XFP 2-Wire Interface tocol</li> <li>Chapter 5: Management interface , Management and diagnost terface</li> <li>Chapter 6: Mechanical and Board definition , Mechanical interincluding guides, EMI shields, module retention, cooling, and e cal connector.</li> <li>Appendix A: Application Reference Model</li> <li>Appendix B: XFI Channel Measurements and Modeling.</li> <li>Appendix C: Differential S-Parameters and TDR</li> <li>Appendix D: Optimum Via Design</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ootprin  |

| <ul> <li>plications (10 Gb/s Ethernet and 10 Gb/s Fibre Channel). Nominal rates range from 9.95 Gb/s, 10.31 Gb/s, 10.52 Gb/s, 10.70 Gb/s, al emerging 11.09 Gb/s. The modules support all data encodings for technologies. The modules may be used to implement single mode multi-mode serial optical interfaces at 850 nm, 1310 nm, or 1550 nm XFP module design may use one of several different optical connects. An adaptable heatsink option allows a single module design compatible with a variety of hosts.</li> <li>The XFP specification includes the following information:</li> <li>XFP reference model and description 3.2</li> <li>Chapter 2: XFP Electrical Interface, Low Speed Electrical Interface Gb/s serial electrical specification (XFI)</li> <li>Chapter 4: XFP 2-Wire Interface Protocol., XFP 2-Wire Interface tocol</li> <li>Chapter 5: Management interface, Management and diagnost terface</li> <li>Chapter 6: Mechanical and Board definition, Mechanical inter including guides, EMI shields, module retention, cooling, and e cal connector.</li> <li>Appendix A: Application Reference Model</li> <li>Appendix B: XFI Channel Measurements and Modeling.</li> <li>Appendix C: Differential S-Parameters and TDR.</li> <li>Appendix D: Optimum Via Design.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| <ul> <li>rates range from 9.95 Gb/s, 10.31 Gb/s, 10.52 Gb/s, 10.70 Gb/s, al emerging 11.09 Gb/s. The modules support all data encodings for technologies. The modules may be used to implement single module multi-mode serial optical interfaces at 850 nm, 1310 nm, or 1550 nm XFP module design may use one of several different optical connet 5.17. An adaptable heatsink option allows a single module design compatible with a variety of hosts.</li> <li>The XFP specification includes the following information:</li> <li>XFP reference model and description <u>3.2</u></li> <li>Chapter 2: XFP Electrical Interface , Low Speed Electrical Inter Gb/s serial electrical specification (XFI)</li> <li>Chapter 3: High Speed Electrical Specification XFI , High speet Gb/s serial electrical specification (XFI)</li> <li>Chapter 5: Management interface , Management and diagnost terface</li> <li>Chapter 6: Mechanical and Board definition , Mechanical inter including guides, EMI shields, module retention, cooling, and e cal connector.</li> <li>Appendix A: Application Reference Model</li> <li>Appendix B: XFI Channel Measurements and Modeling.</li> <li>Appendix C: Differential S-Parameters and TDR</li> <li>Appendix D: Optimum Via Design</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •        |

| <ul> <li>emerging 11.09 Gb/s. The modules support all data encodings for technologies. The modules may be used to implement single mode multi-mode serial optical interfaces at 850 nm, 1310 nm, or 1550 nm XFP module design may use one of several different optical connet 5.17. An adaptable heatsink option allows a single module design compatible with a variety of hosts.</li> <li>The XFP specification includes the following information:</li> <li>XFP reference model and description <u>3.2</u></li> <li>Chapter 2: XFP Electrical Interface, Low Speed Electrical Interface Chapter 3: High Speed Electrical Specification XF1, High speed Gb/s serial electrical specification (XFI)</li> <li>Chapter 4: XFP 2-Wire Interface Protocol, XFP 2-Wire Interface tocol</li> <li>Chapter 5: Management interface, Management and diagnost terface</li> <li>Chapter 6: Mechanical and Board definition, Mechanical interincluding guides, EMI shields, module retention, cooling, and e cal connector.</li> <li>Appendix A: Application Reference Model</li> <li>Appendix B: XFI Channel Measurements and Modeling.</li> <li>Appendix C: Differential S-Parameters and TDR</li> <li>Appendix D: Optimum Via Design</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

| <ul> <li>multi-mode serial optical interfaces at 850 nm, 1310 nm, or 1550 nm XFP module design may use one of several different optical connects for the several difference optical connects of the several difference optical connect</li></ul> | or these |

| <ul> <li>XFP module design may use one of several different optical connects.</li> <li>XFP module design may use one of several different optical connects.</li> <li>The XFP specification includes the following information:</li> <li>XFP reference model and description <u>3.2</u></li> <li>Chapter 2: XFP Electrical Interface, Low Speed Electrical Interface.</li> <li>Chapter 3: High Speed Electrical Specification XFI, High spee Gb/s serial electrical specification (XFI)</li> <li>Chapter 4: XFP 2-Wire Interface Protocol, XFP 2-Wire Interface tocol</li> <li>Chapter 5: Management interface, Management and diagnost terface</li> <li>Chapter 6: Mechanical and Board definition, Mechanical interincluding guides, EMI shields, module retention, cooling, and e cal connector.</li> <li>Appendix A: Application Reference Model</li> <li>Appendix B: XFI Channel Measurements and Modeling.</li> <li>Appendix D: Optimum Via Design.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| <ul> <li>5.17. An adaptable heatsink option allows a single module design compatible with a variety of hosts.</li> <li>The XFP specification includes the following information:</li> <li>XFP reference model and description <u>3.2</u></li> <li>Chapter 2: XFP Electrical Interface, Low Speed Electrical Interface Chapter 3: High Speed Electrical Specification XFI, High speed Gb/s serial electrical specification (XFI)</li> <li>Chapter 4: XFP 2-Wire Interface Protocol, XFP 2-Wire Interface tocol</li> <li>Chapter 5: Management interface, Management and diagnost terface</li> <li>Chapter 6: Mechanical and Board definition, Mechanical interincluding guides, EMI shields, module retention, cooling, and e cal connector.</li> <li>Appendix A: Application Reference Model</li> <li>Appendix B: XFI Channel Measurements and Modeling.</li> <li>Appendix C: Differential S-Parameters and TDR</li> <li>Appendix D: Optimum Via Design.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| <ul> <li>The XFP specification includes the following information:</li> <li>XFP reference model and description <u>3.2</u></li> <li><u>Chapter 2: XFP Electrical Interface</u>, Low Speed Electrical Interface</li> <li><u>Chapter 3: High Speed Electrical Specification XFI</u>, High speed Gb/s serial electrical specification (XFI)</li> <li><u>Chapter 4: XFP 2-Wire Interface Protocol</u>, XFP 2-Wire Interface tocol</li> <li><u>Chapter 5: Management interface</u>, Management and diagnost terface</li> <li><u>Chapter 6: Mechanical and Board definition</u>, Mechanical interincluding guides, EMI shields, module retention, cooling, and e cal connector.</li> <li>Appendixes providing implementation and measurement suggetions.</li> <li><u>Appendix A: Application Reference Model</u></li> <li><u>Appendix B: XFI Channel Measurements and Modeling</u></li> <li><u>Appendix C: Differential S-Parameters and TDR</u>.</li> <li><u>Appendix D: Optimum Via Design</u>.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| <ul> <li>XFP reference model and description <u>3.2</u></li> <li><u>Chapter 2: XFP Electrical Interface</u>, Low Speed Electrical Interface</li> <li><u>Chapter 3: High Speed Electrical Specification XFI</u>, High speed Gb/s serial electrical specification (XFI)</li> <li><u>Chapter 4: XFP 2-Wire Interface Protocol</u>, XFP 2-Wire Interface tocol</li> <li><u>Chapter 5: Management interface</u>, Management and diagnost terface</li> <li><u>Chapter 6: Mechanical and Board definition</u>, Mechanical interincluding guides, EMI shields, module retention, cooling, and e cal connector.</li> <li>Appendixes providing implementation and measurement suggetions.</li> <li><u>Appendix A: Application Reference Model</u></li> <li><u>Appendix B: XFI Channel Measurements and Modeling</u></li> <li><u>Appendix C: Differential S-Parameters and TDR</u></li> <li><u>Appendix D: Optimum Via Design</u></li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |